### **About the Author**

A Nagoor Kani is a multifaceted personality with efficient technical expertise and management skills. He obtained his BE degree in Electrical and Electronics Engineering from Thiagarajar College of Engineering, Madurai, and MS (Electronics and Control) through Distance Learning program of BITS, Pilani. He is a life member of ISTE and IETE.

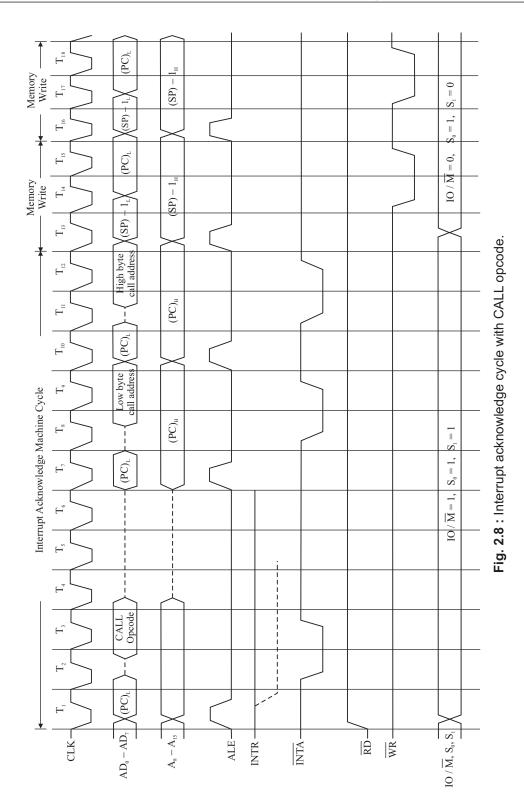

He started his career as a self-employed industrialist (1986-1989) and then changed over to teaching in 1989. He has worked as Lecturer in Dr MGR Engineering College (1989-1990) and as Asst. Professor in Satyabhama Engineering College (1990-1997). In 1993, he started a teaching centre for BE students named Institute of Electrical Engineering, which was renamed RBA Tutorials in 2005.

A Nagoor Kani launched his own organization in 1997. The ventures currently run by him are RBA engineering (involved in manufacturing of lab equipments, microprocessor trainer kits and undertake Electrical contracts and provide electrical consultancy), RBA Innovations (involved in developing projects for engineering students and industries), RBA Tutorials (conducting tutorial classes for engineering students and coaching for GATE, IES, IAS) and RBA Publications (publishing of engineering books), RBA Software (involved in web-design and maintenance). His optimistic and innovative ideas have made the RBA Group a very successful venture.

A Nagoor Kani is a well-known name in major engineering colleges in India. He is an eminent writer and till now he has authored several engineering books (published by Tata McGraw Hill Education and RBA Publications) which are very popular among engineering students. He has written books in the areas of Control Systems, Signals and Systems, Microcontrollers, Digital Signal Processing, Electric Circuits, Electrical Machines and Power Systems.

### THIRD EDITION

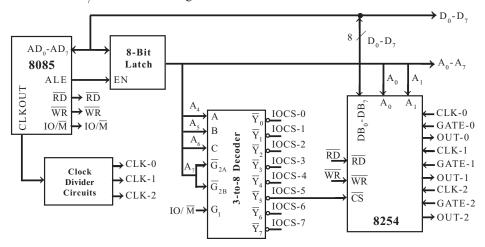

A Nagoor Kani

Founder RBA Group Chennai

#### Tata McGraw Hill

Published by the Tata McGraw Hill Education Private Limited, 7 West Patel Nagar, New Delhi 110 008.

# Dedicated to my

Brother-in-law Mr. K. Abdul Rawoof, M.A.

Sister Mrs. A. Mumtaj Rawoof, B.Sc. and

Their Daughter Dr. A. Shafela Sherin, B.D.S. and

Son Dr. A. Mohammed Fazil, M.B.B.S.

The **McGraw**·Hill Companies

## **CONTENTS**

| Preface  |          | xii  |

|----------|----------|------|

| Acknowle | dgements | xiii |

#### CHAPTER - 1 INTRODUCTION TO MICROPROCESSOR

| 1.1     | Terms used in microprocessor literature     | 1. 1 |

|---------|---------------------------------------------|------|

| 1.2     | Evolution of microprocessor                 | 1. 3 |

| 1.3     | Basic functional blocks of a microprocessor | 1. 6 |

| 1.4     | Microprocessor-based system                 | 1.7  |

|         | (Organization of microcomputer)             |      |

| 1.5     | Concept of multiplexing in microprocessor   | 1.9  |

| 1.6     | Micro, Mini and Large computers             | 1.9  |

| 1.7     | INTEL 8085                                  | 1.12 |

| 1.8     | INTEL 8086                                  | 1.20 |

| 1.9     | ZILOG Z80                                   | 1.29 |

| 1.10    | MOTOROLA 6800                               | 1.33 |

| 1.11    | Summary                                     | 1.36 |

| 1.12    | Short questions and answers                 | 1.38 |

| CHAPTER | R - 2 INSTRUCTION SET OF 8085               |      |

| 21      | Origin of software                          | 2 1  |

| 22      | Durana anala                                | 2 1  |

| <i>L</i> . <i>L</i> | 1 Tocessor cycles          | 2. 1 |

|---------------------|----------------------------|------|

| 23                  | Machine cycles of 8085     | 2 1  |

|                     | 2.3.1 Timing diagram 2.2   |      |

| 24                  | Instruction format of 8085 | 211  |

| 25                  | Addressing modes           | 211  |

| 26                  | Instruction set            | 2.12 |

viii

| 2.    | 7 Data transfer instructions                         | 2.21 |

|-------|------------------------------------------------------|------|

| 2.    | 8 Arithmetic instructions                            | 2.29 |

| 2.    | 9 Logical instructions                               | 2.36 |

| 2     | 10 Branching instructions                            | 2.43 |

| 2     | 11 Machine control instructions                      | 2.46 |

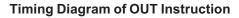

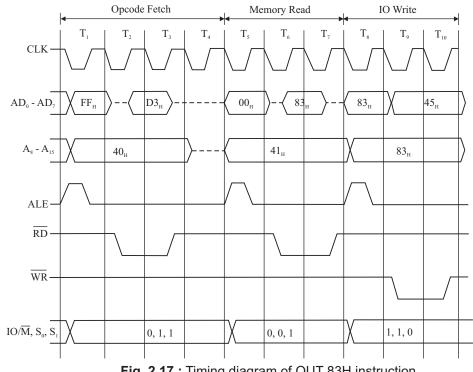

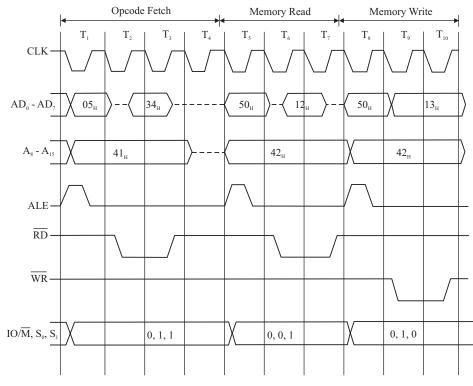

| 2     | 12 Timing diagram of 8085 instructions               | 2.48 |

| 2     | 13 Summary                                           | 2.57 |

| 2.    | 14 Short questions and answers                       | 2.57 |

| CHAPT | ER - 3 MEMORY AND IO INTERFACING                     |      |

| З.    | 1 Introduction to memory                             | 3. 1 |

| З.    | 2 Semiconductor memory                               | 3. 1 |

| З.    | 3 ROM and PROM                                       | 3. 3 |

| З.    | 4 EPROM                                              | 3. 4 |

| З.    | 5 Static RAM                                         | 3.7  |

| З.    | 6 DRAM and NVRAM                                     | 3.11 |

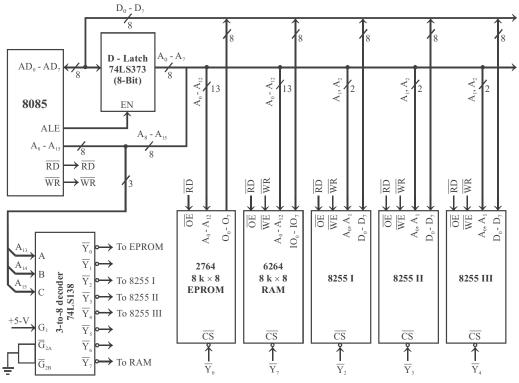

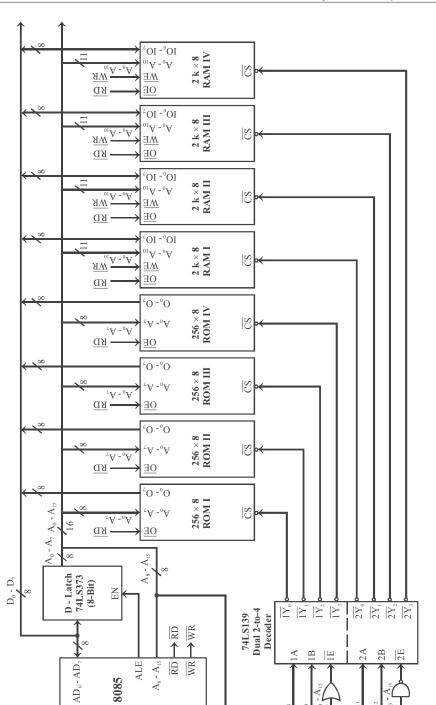

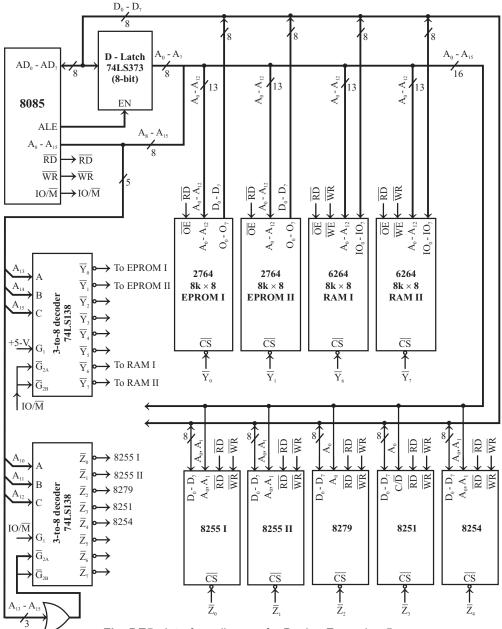

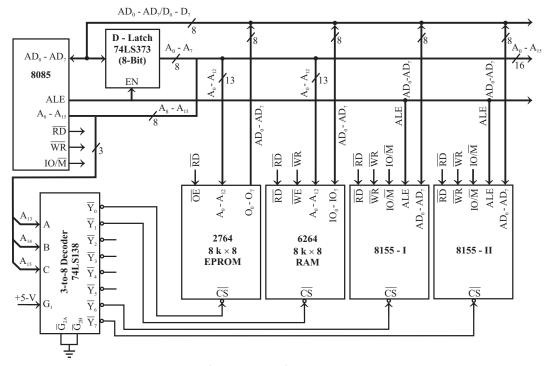

| З.    | 7 Interfacing static RAM and EPROM                   | 3.12 |

| З.    | 8 Memory organization in 8085-based system           | 3.16 |

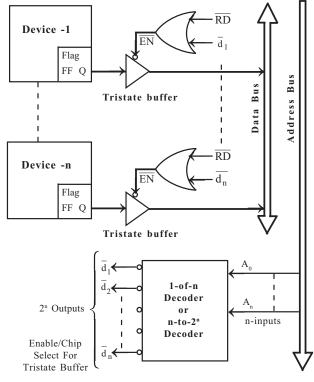

| З.    | 9 10 structure of a typical microcomputer            | 3.19 |

| З.    | 10 Interfacing IO and peripheral devices             | 3.20 |

| З.    | 11 Summary                                           | 3.37 |

| З.    | 12 Short questions and answers                       | 3.38 |

| CHAPT | ER - 4 INTERRUPTS                                    |      |

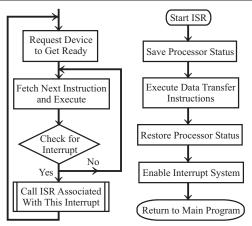

| 4.    | 1 Interrupt and its need                             | 4. 1 |

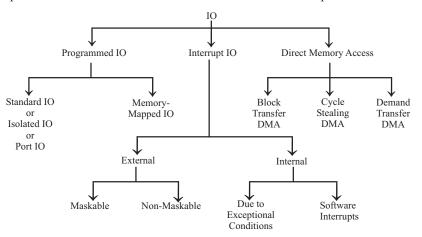

| 4.    | 2 Classification of interrupts                       | 4. 2 |

| 4.    | 3 Interrupts of 8085                                 | 4.3  |

|       | 4.3.1 Software interrupts of 8085 4.3                |      |

|       | 4.3.2 Hardware interrupts of 8085 4.4                |      |

|       | 4.3.3 Priorities of interrupts of 8085 4.5           |      |

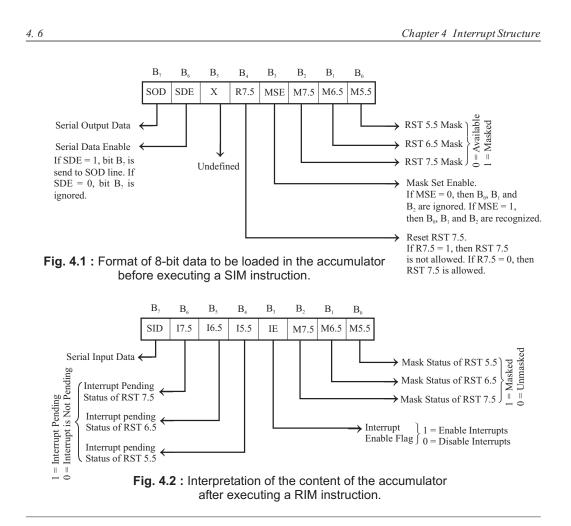

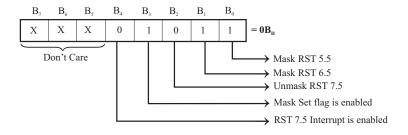

| 4.    | 4 Enabling, disabling and masking of 8085 interrupts | 4.5  |

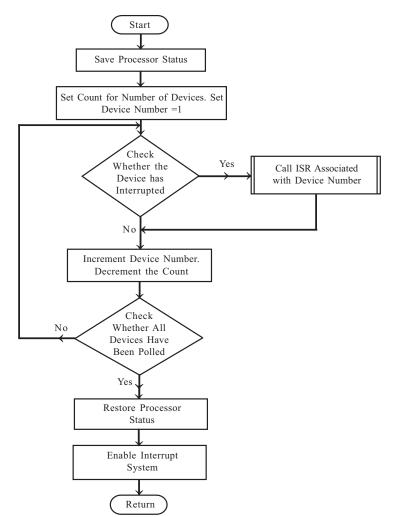

| 4.5 | Polling of interrupts                                | 4. 7 |

|-----|------------------------------------------------------|------|

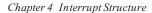

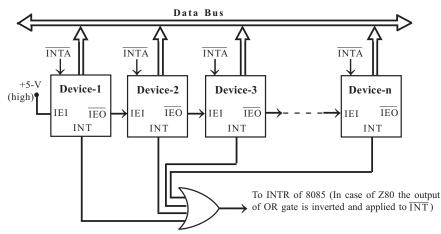

| 4.6 | INTR and its expansion                               | 4.11 |

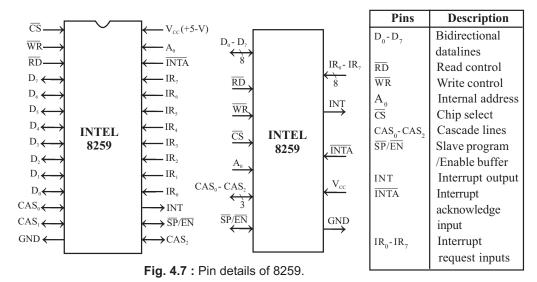

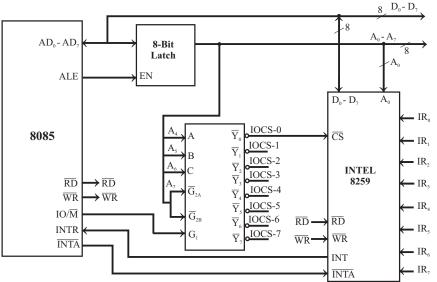

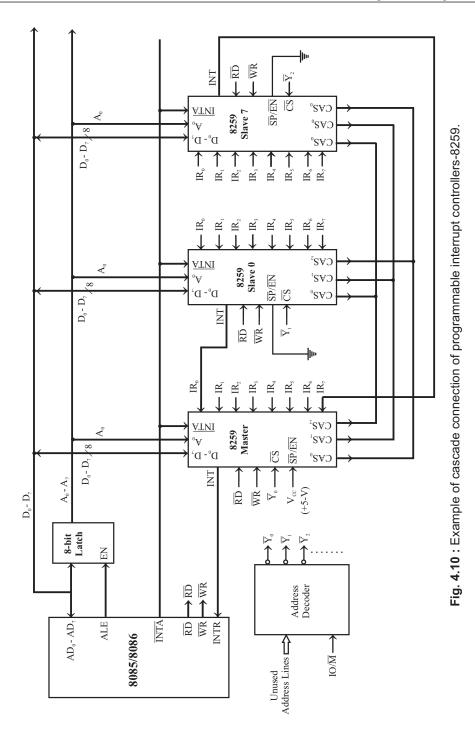

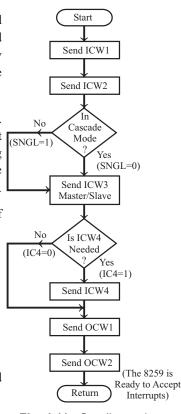

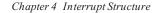

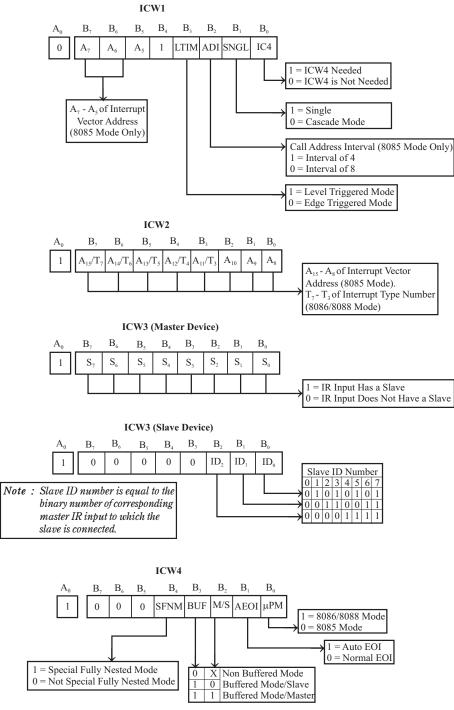

| 4.7 | Programmable interrupt controller - INTEL 8259       | 4.12 |

|     | 4.7.1 Interfacing 8259 with 8085 microprocessor 4.13 |      |

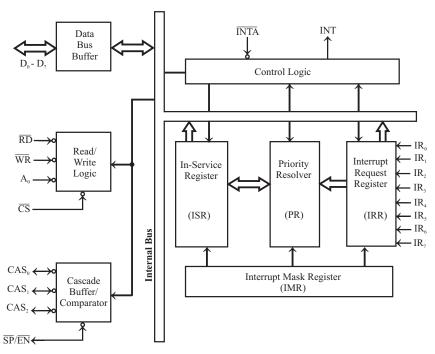

|     | 4.7.2 Functional block diagram of 8259 4.15          |      |

|     | 4.7.3 Processing of interrupts by 8259 4.17          |      |

|     | 4.7.4 Programming 8259(or initializing 8259) 4.18    |      |

| 4.8 | Summary                                              | 4.22 |

| 4.9 | Short questions and answers                          | 4.23 |

|     |                                                      |      |

iх

#### CHAPTER - 5 ASSEMBLY LANGUAGE PROGRAMMING

| 5.1     | Levels of programming                                      | 5. 1 |  |  |  |  |

|---------|------------------------------------------------------------|------|--|--|--|--|

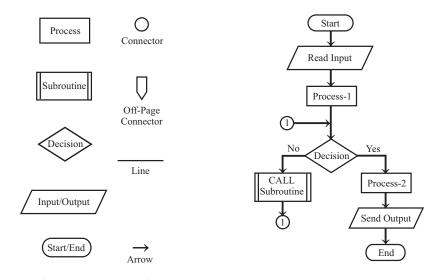

| 5.2     | Flowchart                                                  | 5.2  |  |  |  |  |

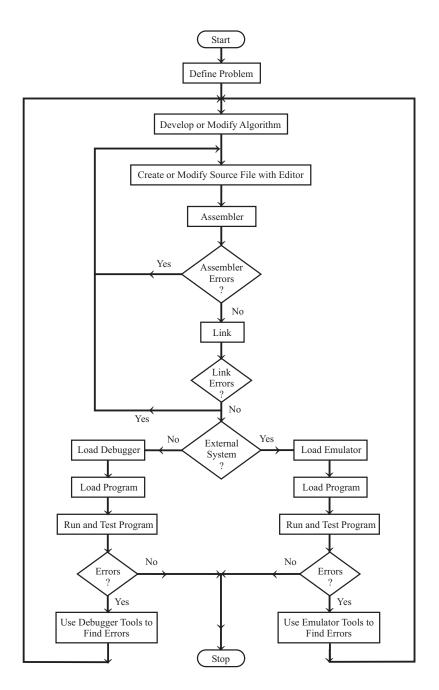

| 5.3     | Assembly language program development tools                | 5.3  |  |  |  |  |

| 5.4     | Variables and constants used in assemblers                 | 5.8  |  |  |  |  |

| 5.5     | Assembler directives                                       | 5.9  |  |  |  |  |

| 5.6     | Procedure and Macro                                        | 5.11 |  |  |  |  |

| 5.7     | Delay routine                                              | 5.12 |  |  |  |  |

| 5.8     | List and array                                             | 5.15 |  |  |  |  |

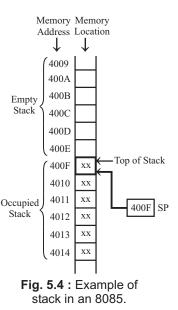

| 5.9     | Stack                                                      | 5.16 |  |  |  |  |

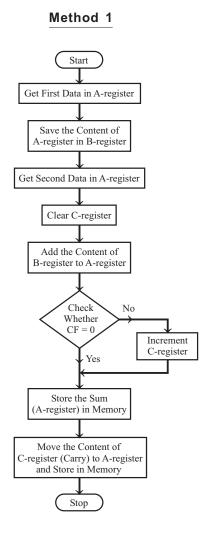

| 5.10    | Examples of 8085 assembly language programs                | 5.17 |  |  |  |  |

| 5.11    | Summary                                                    |      |  |  |  |  |

| 5.12    | Short questions and answers                                |      |  |  |  |  |

| CHAPTER | - 6 PERIPHERAL DEVICES AND INTERFACING                     | 6. 1 |  |  |  |  |

| 6.1     | Programmable peripheral devices                            | 6. 1 |  |  |  |  |

| 6.2     | Parallel data communication interface                      | 6. 1 |  |  |  |  |

|         | 6.2.1 Parallel data transfer schemes 6.2                   |      |  |  |  |  |

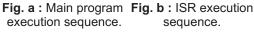

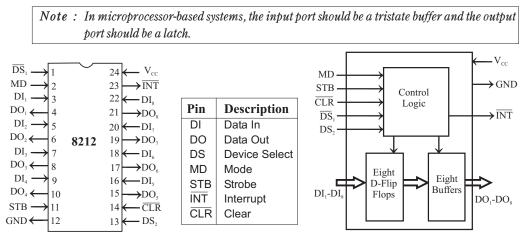

|         | 6.2.2 INTEL 8212 6.4                                       |      |  |  |  |  |

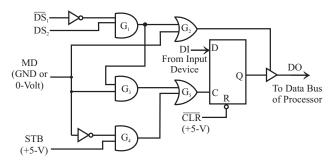

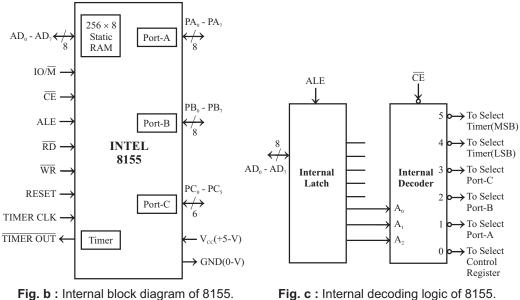

|         | 6.2.3 Programmable 10 port and timer - INTEL 8155/8156 6.6 |      |  |  |  |  |

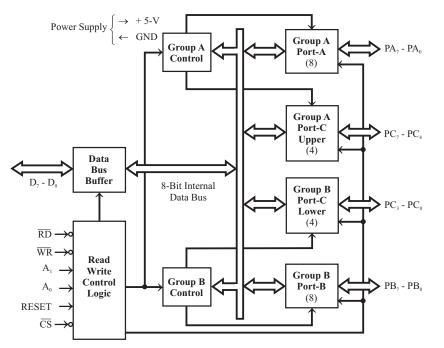

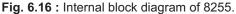

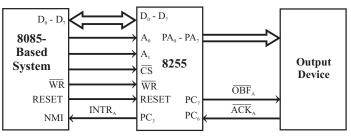

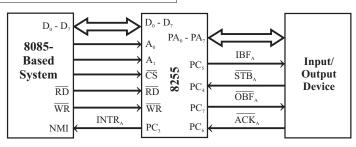

|         | 6.2.4 Programmable peripheral interface - INTEL 8255 6.12 |             |  |

|---------|-----------------------------------------------------------|-------------|--|

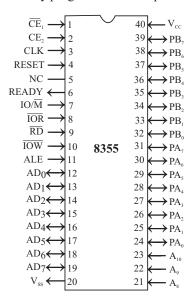

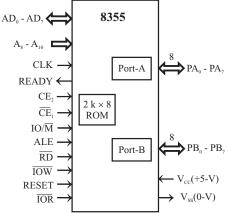

|         | 6.2.5 Programmable IO port and memory - INTEL 8355 6.20   |             |  |

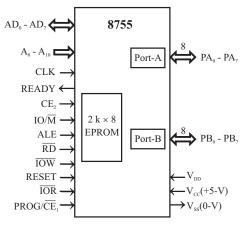

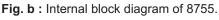

|         | 6.2.6 Programmable IO port and memory - INTEL 8755 6.21   |             |  |

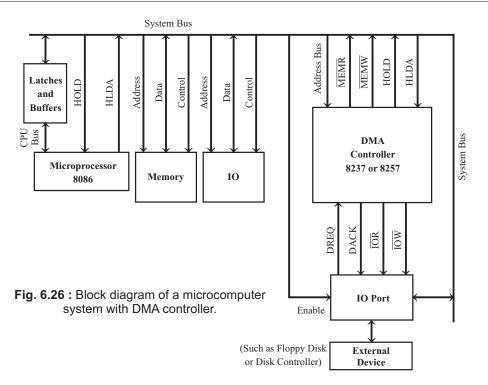

|         | 6.2.7 DMA data transfer scheme 6.22                       |             |  |

|         | 6.2.8 DMA controller - INTEL 8237 6.24                    |             |  |

|         | 6.2.9 DMA controller - INTEL 8257 6.37                    |             |  |

| 6.3     | Serial data communication interface                       | 6.45        |  |

|         | 6.3.1 Serial data communication 6.45                      |             |  |

|         | 6.3.2 USART - INTEL 8251A 6.50                            |             |  |

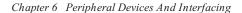

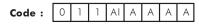

| 6.4     | Keyboard and display interface                            | 6.55        |  |

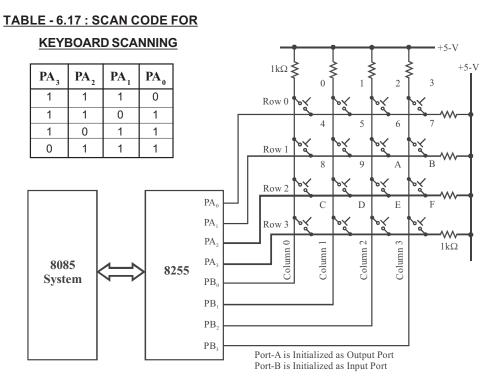

|         | 6.4.1 Keyboard interface using ports 6.55                 |             |  |

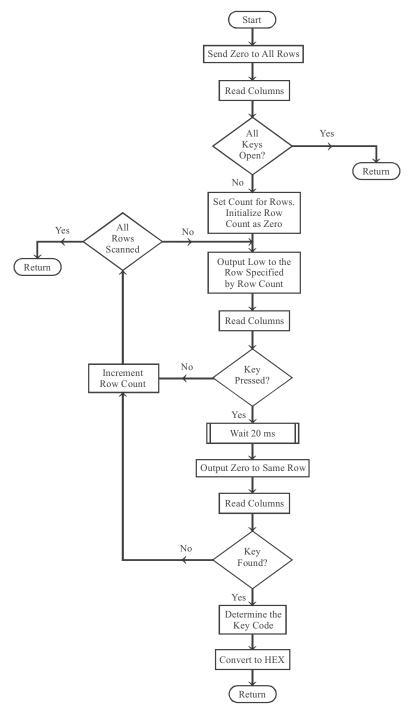

|         | 6.4.2 Display interface using ports 6.58                  |             |  |

|         | 6.4.3 Latches and buffers as IO devices 6.63              |             |  |

|         | 6.4.4 Keyboard/Display controller - INTEL 8279 6.65       |             |  |

|         | 6.4.5 Keyboard and display interface using 8279 6.69      |             |  |

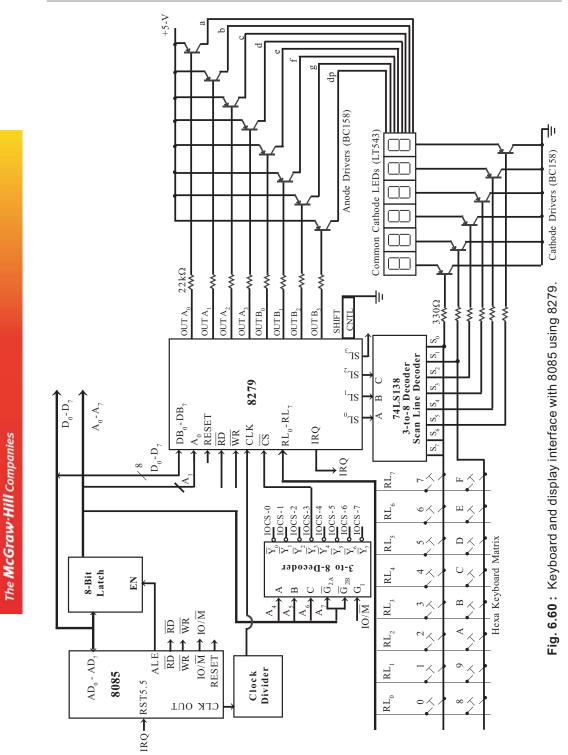

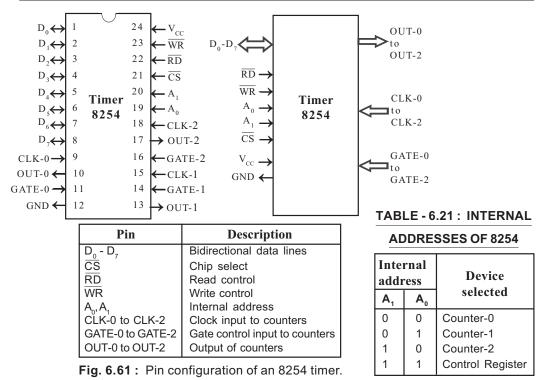

| 6.5     | Programmable timer - INTEL 8254                           | <i>6.72</i> |  |

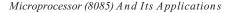

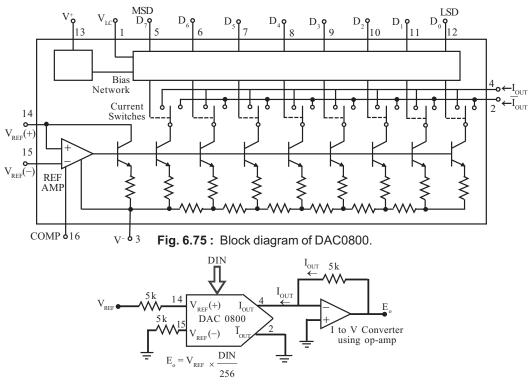

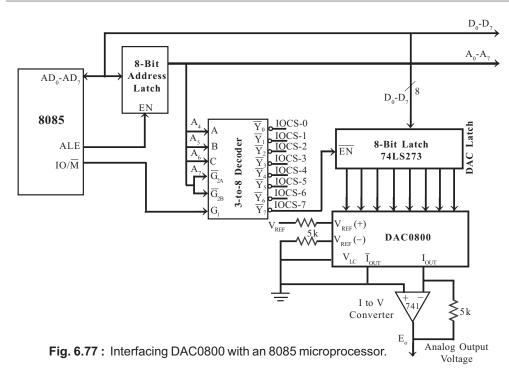

| 6.6     | DAC interface                                             | 6.82        |  |

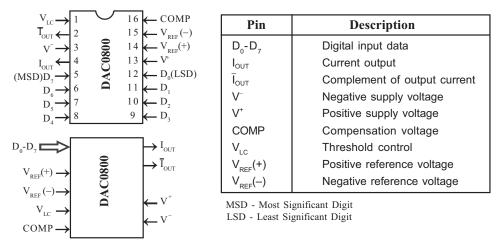

|         | 6.6.1 DAC0800 6.84                                        |             |  |

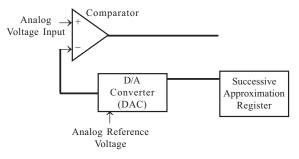

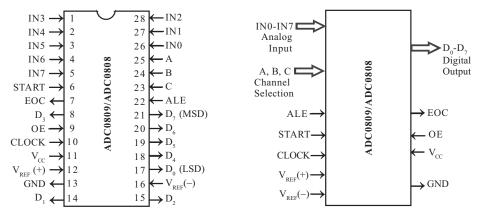

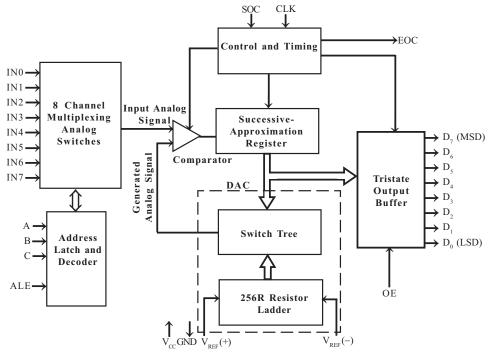

| 6.7     | ADC interface                                             | 6.86        |  |

|         | 6.7.1 ADC0809 6.88                                        |             |  |

| 6.8     | Summary                                                   | 6.92        |  |

| 6.9     | Short questions and answers                               | 6.94        |  |

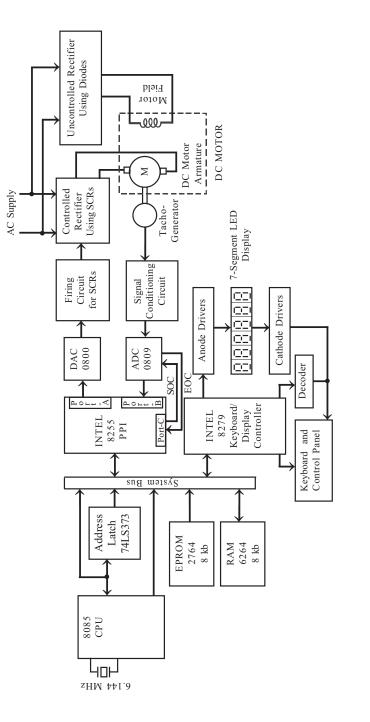

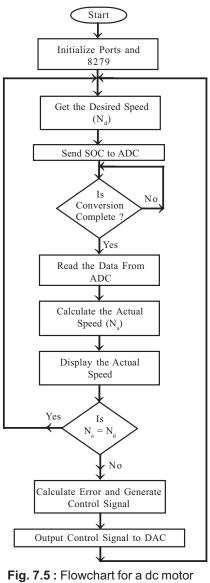

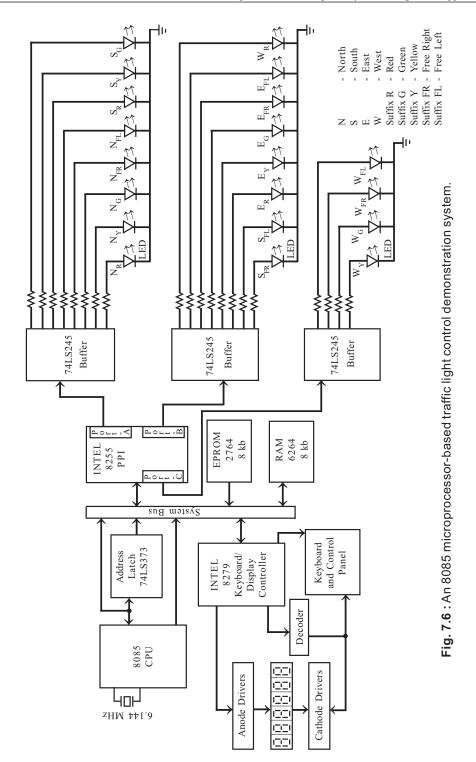

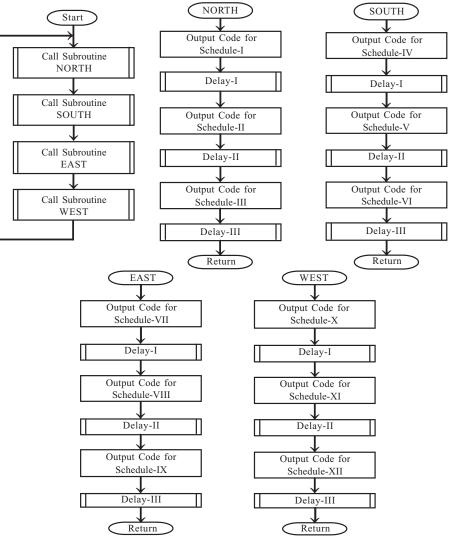

| CHAPTER | - 7 MICROCOMPUTER SYSTEM DESIGN AND APPLICATIONS          |             |  |

| 7.1     | Designing a microprocessor-based system                   | 7. 1        |  |

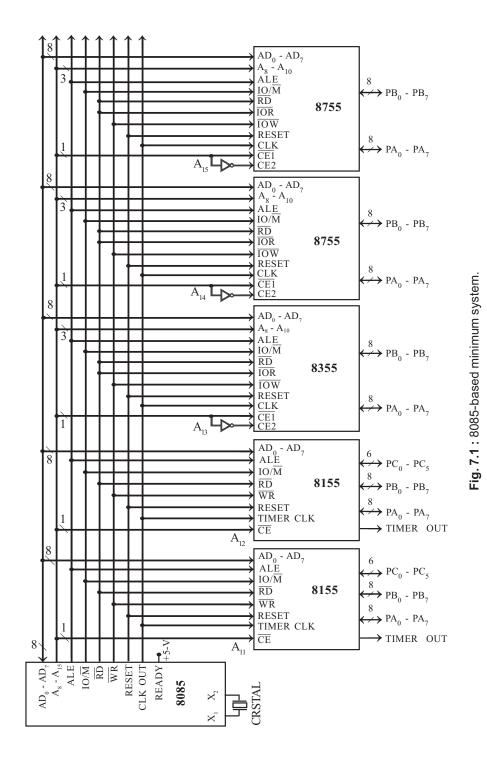

| 7.2     | 8085-based minimum system                                 | 7. <i>3</i> |  |

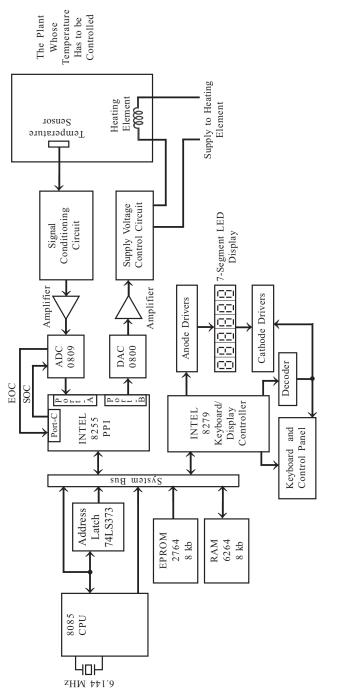

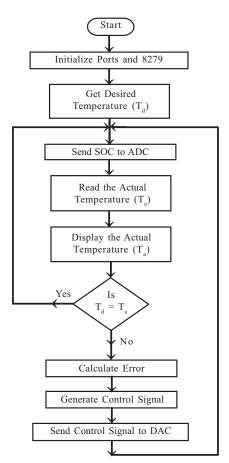

| 7.3     | Temperature control system                                |             |  |

| 7.4     | Motor speed control system                                | 7.7         |  |

| 7.5  | Traffic light control system                       | 7. 9       | 9 |

|------|----------------------------------------------------|------------|---|

| 7.6  | Stepper motor control system                       | 7.1        | 3 |

| APPE | NDIX I 8085A instructions in hexadecimal order     | <i>A</i> . | 1 |

| APPE | NDIX II 8085A instructions in alphabetical order   | А.         | 3 |

| APPE | NDIX III List of microprocessors released by INTEL | А.         | 5 |

| GEN  | ERAL INDEX                                         | Ι.         | 1 |

| CHIF | P INDEX                                            | I.         | 5 |

#### xi

## Preface

The main objective of this book is to explore the basic concepts of most popular INTEL 8085 microprocessor and its programming and interfacing techniques in a simple and easy-to-understand manner.

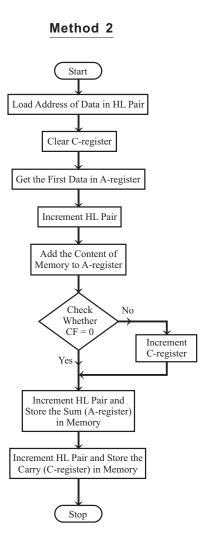

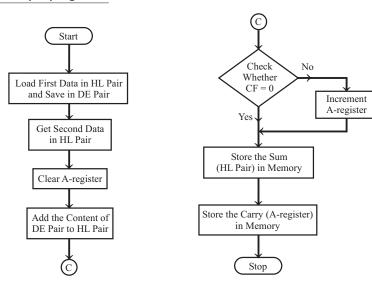

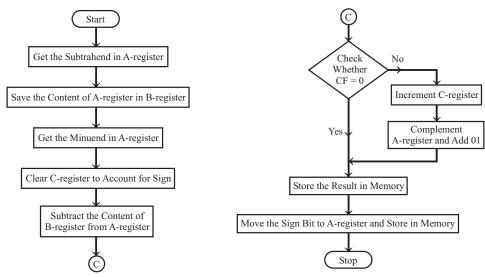

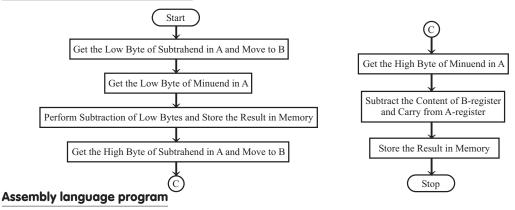

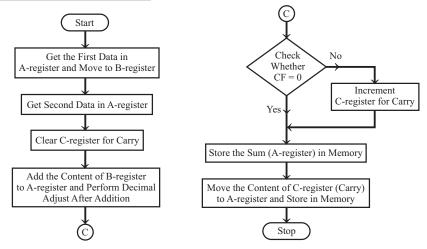

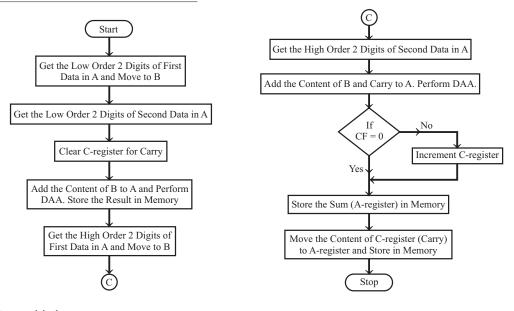

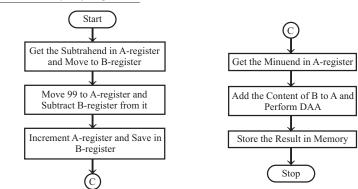

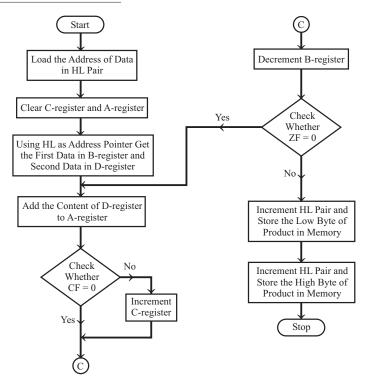

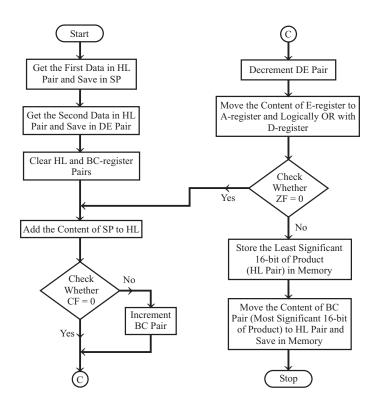

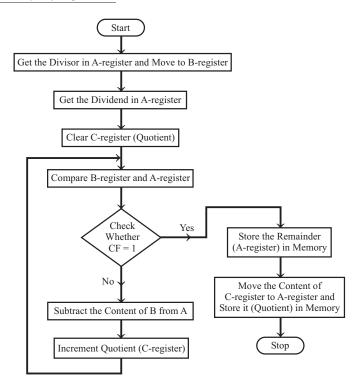

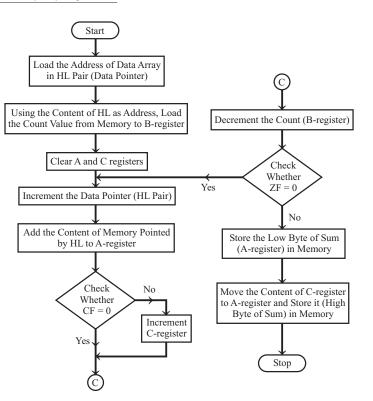

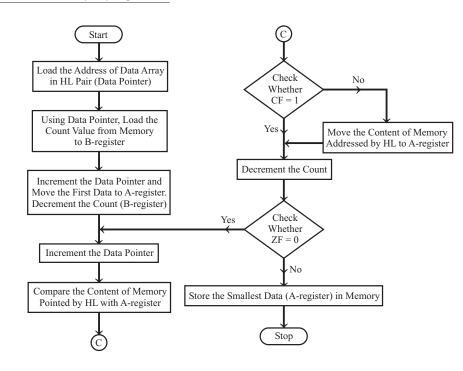

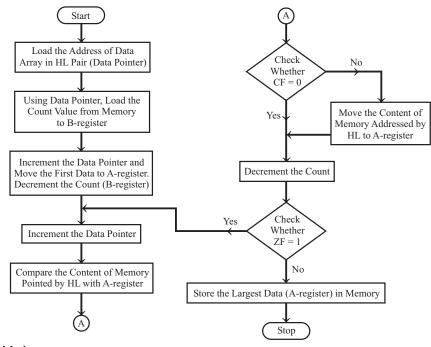

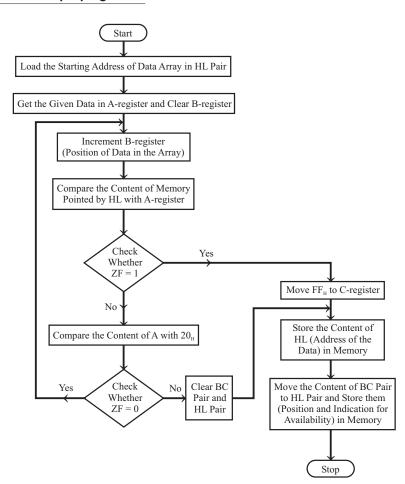

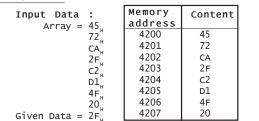

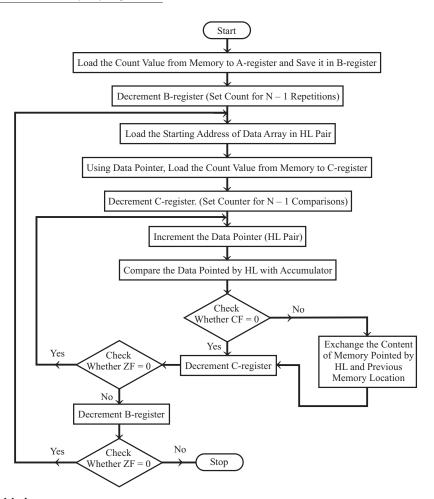

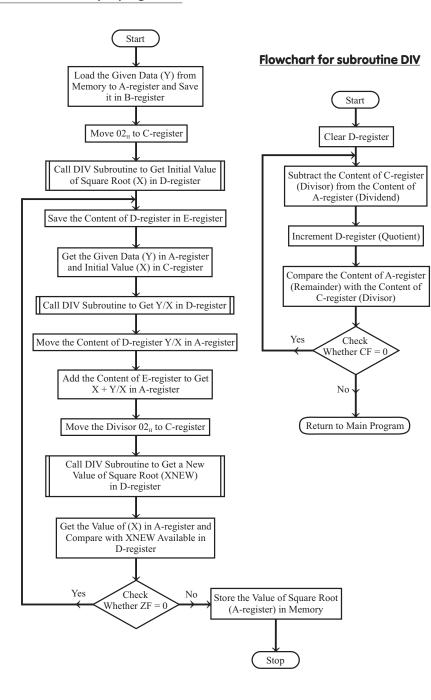

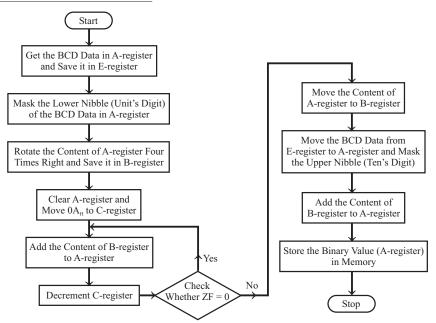

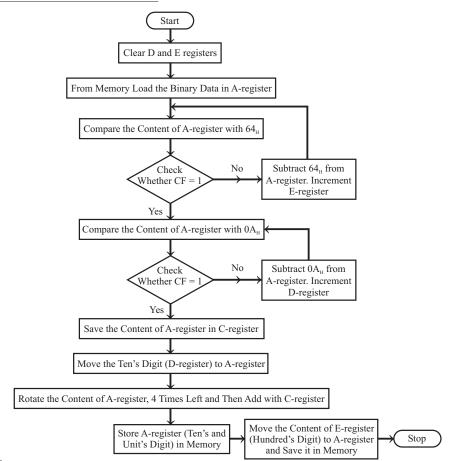

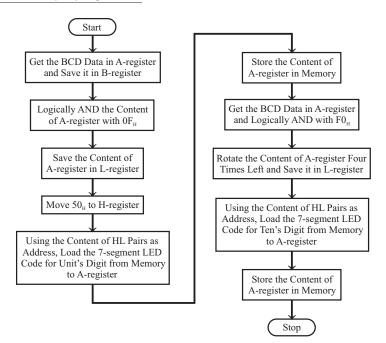

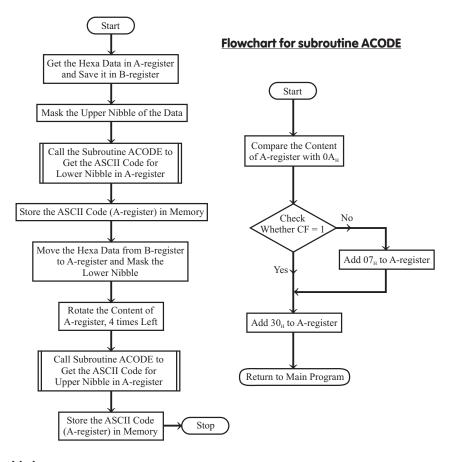

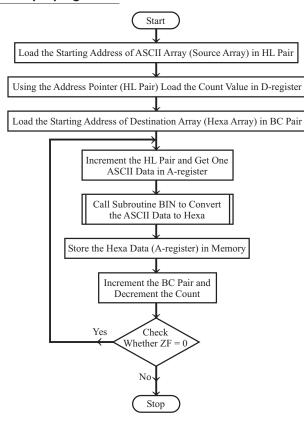

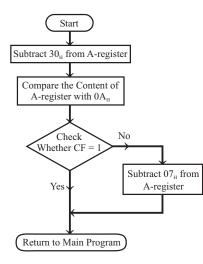

This text on 8085 microprocessor has been crafted and designed to meet student's requirements. Considering the complex technical nature of this subject, equal emphasis has been given to programming and design aspects. Considerable effort has been made to explain the assembly language programs with step-by-step algorithm and flowchart. The peripheral interfacing techniques has been explained with simple sketches clearly showing the necessary signals. Short questions and answers with varied difficulty levels are given in the text to help students get an intuitive grasp on the subject.

This book with its lucid writing style and germane pedagogical features will prove to be a master text for engineering students and practitioners.

The chapter-1 briefs about evolution of microprocessor and basics of microprocessor-based system. An introductory discussion on popular microprocessors 8085, 8086, Z80 and 6800 are presented in chapter-1.

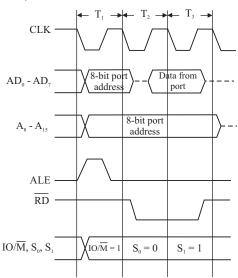

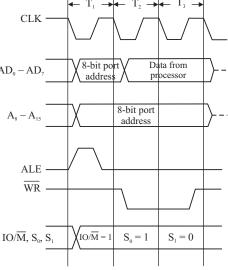

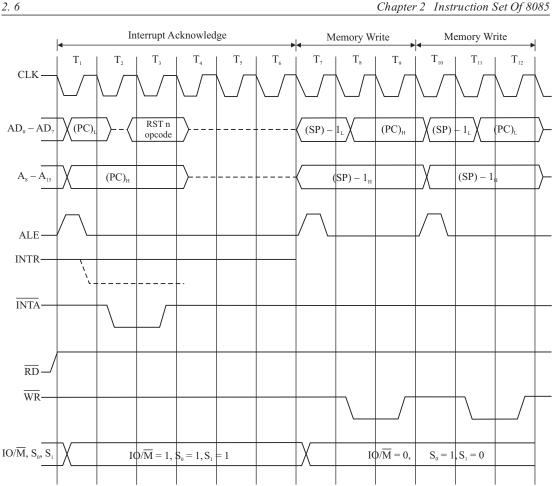

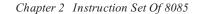

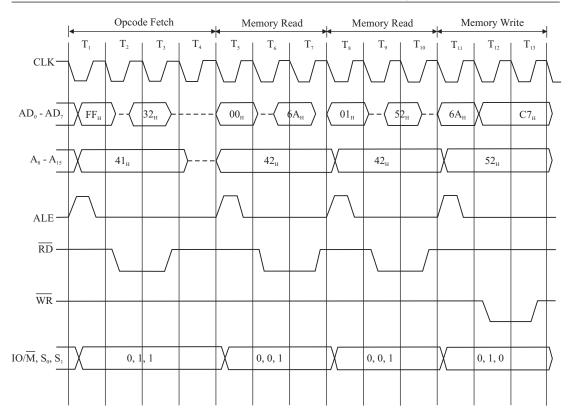

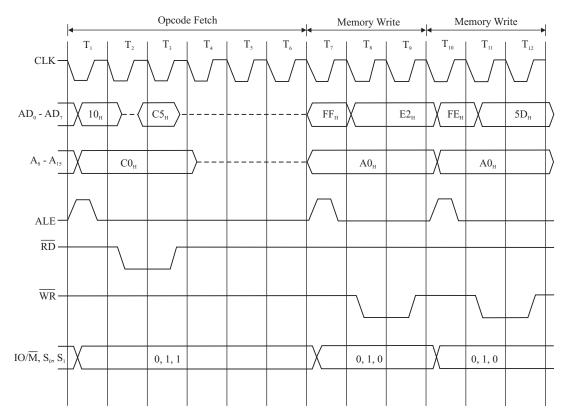

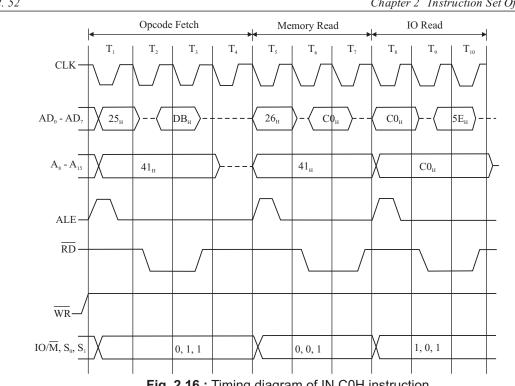

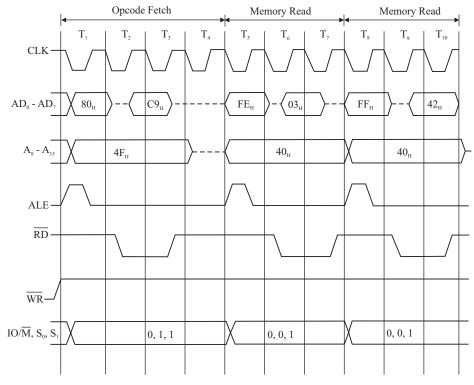

The machine cycles of 8085 processor and their timing diagrams are discussed in chapter-2. Also the instructions of 8085 microprocessor are explained with example in chapter-2.

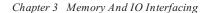

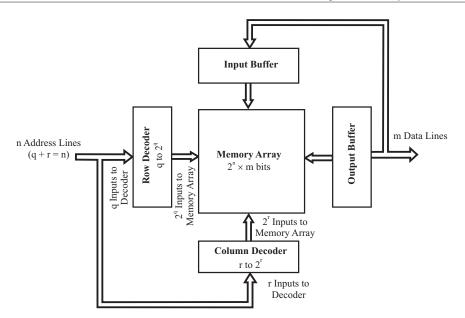

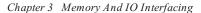

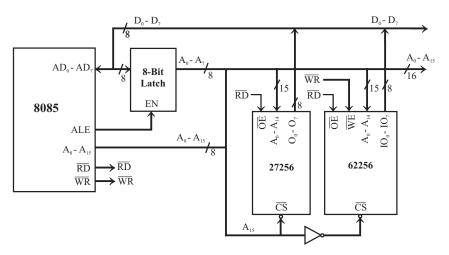

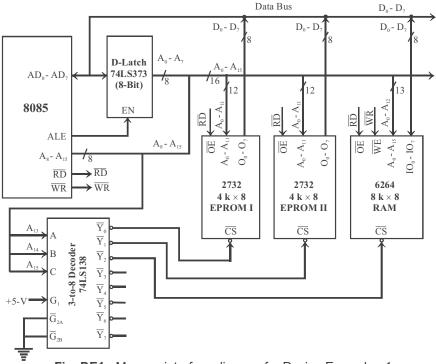

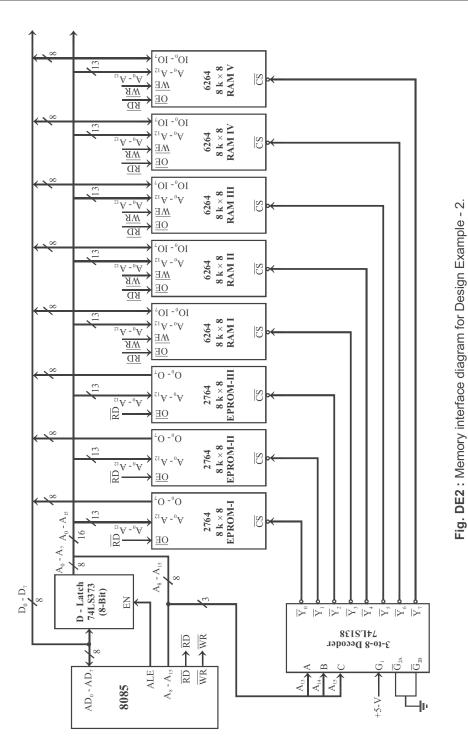

The details of semiconductor memory and their interfacing with 8085 microprocessor are presented in chapter-3. Design examples are also included for better understanding of the concept of the memory and IO interfacing with 8085 microprocessor.

The importance of interrupts and their implementation in 8085 system are discussed in chapter-4. Methods for expanding the interrupts of 8085 are also discussed in chapter-4.

The concepts of assembly language programming are discussed in chapter-5. A number of assembly language example programs using 8085 microprocessor instructions are included in this chapter. These example programs are assembled using X8085A assembler and verified in RBA-8085 trainer kit.

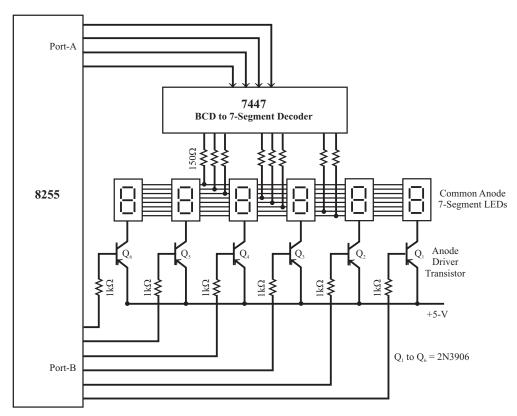

The concepts of port, keyboard and 7-segment display and their interfacing are discussed in chapter-6. Simple discussions about USART, DMA controllers, Programmable timer, ADC and DAC, and their interfacing with 8085 microprocessor are also presented in chapter-6.

Some of the 8085 microprocessor-based systems for specific applications are discussed in chapter-7. The 8085 microprocessor instructions along with their opcodes are listed in Appendix-I and Appendix-II as ready reference for assembly language programmers.

The author has taken care to present the concepts of microprocessor in a way easy to grasp by students. The readers can feel free to convey their criticism and suggestions to kani@vsnl.com for further improvement of the book.

#### A. Nagoor Kani

### Acknowledgements

I express my heartful thanks to my wife Ms C Gnanaparanjothi Nagoor Kani and my sons N Bharath Raj alias Chandrakani Allaudeen and N Vikram Raj for the support, encouragement and cooperation they have extended to me throughout my career.

It is my pleasure to acknowledge the contributions to our technical editors,

Ms B Hemavathy, Ms S Pavithra, Ms K Thangaselvi for editing and proofreading of the manuscript, and Ms A Selvi, Ms M Faritha for type setting and preparing the layout of the book.

My sincere thanks to all reviewers for their valuable suggestions and comments which helps me to explore the subject to greater depth.

I am also grateful to Ms Vibha Mahajan, Mr Ebi John, Ms Smruti Snigha, Ms Nimisha Kapoor, Ms Koyel Ghosh, Mr P L Pandita, Ms Sohini Mukherjee, ..... and ..... of Tata McGraw Hill Education for their concern and care in publishing this work.

My special thanks to Ms. Smruti Snigha of McGraw Hill Education for her care in bringing out this work at the right time.

I thank all my office staff for their co-operation in carrying out my day-to-day activities.

Finally, a special note of appreciation is due to my sisters, brothers, relatives, friends, students and the entire teaching community for their overwhelming support and encouragement to my writing.

A. Nagoor Kani

The **McGraw**·Hill Companies

## CHAPTER

## **INTRODUCTION TO MICROPROCESSOR**

#### 1.1 TERMS USED IN MICROPROCESSOR LITERATURE

| Bit                                     | : | A digit of the binary number or code is called bit.                                                                                                                                    |

|-----------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nibble                                  | : | The 4-bit (4-digit) binary number or code is called nibble.                                                                                                                            |

| Byte                                    | : | The 8-bit (8-digit) binary number or code is called byte.                                                                                                                              |

| Word                                    | : | The 16-bit (16-digit) binary number or code is called word.                                                                                                                            |

| Double Word                             | : | The 32-bit (32-digit) binary number or code is called double word.                                                                                                                     |

| Multiple Word                           | : | The 64, 128, bit/digit binary numbers or codes are called multiple words.                                                                                                              |

| Data                                    | : | The quantity (binary number/code) operated by an instruction of a program is called data. The size of data is specified as bit, byte, word, etc.                                       |

| Address                                 | : | Address is an identification number in binary for memory locations.<br>The 8086 processor uses 20-bit address for memory.                                                              |

| Memory Word Size<br>(or Addressability) | : | The memory word size or addressability is the size of binary information<br>that can be stored in a memory location. The memory word size for 8085<br>processor-based system is 8-bit. |

[The address and program codes in microprocessor system are given in binary (i.e., as a combination of "0" and "1"). With n-bit binary we can generate  $2^n$  different binary codes or address.]

| Microprocessor | : | The microprocessor is a program controlled semiconductor device(IC), which fetches (from memory), decodes and executes instructions. It is used as CPU (Central Processing Unit) in computers.                                                                                                                                                                                            |  |

|----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                |   | The basic functional blocks of a microprocessor are ALU (Arithmetic Logic Unit), an array of registers and a control unit. The microprocessor is identified with the size of data, and the ALU of the processor it can work with at a time. The 8085 processor has 8-bit ALU, hence it is called 8-bit processor. The 8086 processor has 16-bit ALU, hence it is called 16-bit processor. |  |

| Bus            | : | A bus is a group of conducting lines that carries data, addresses and control signals. Buses can be classified into Data bus, Address bus and Control bus.                                                                                                                                                                                                                                |  |

|                |   | The group of conducting lines that carries data is called data bus.                                                                                                                                                                                                                                                                                                                       |  |

|                |   | The group of conducting lines that carries addresses is called address bus.                                                                                                                                                                                                                                                                                                               |  |

|                |   | The group of conducting lines that carries control signals is called control bus.                                                                                                                                                                                                                                                                                                         |  |

| 1. 2       | Chapter 1 Introduction to Microprocessor                                                                                                                                                                                               |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Bus    | : The group of conducting lines that are directly connected to microprocessor<br>is called CPU bus. In a CPU bus the signals are multiplexed, i.e., more<br>than one signal are passed through the same line but at different timings. |

| System Bus | : The group of conducting lines that carries data, addresses and control signals in a microcomputer system is called system bus. Multiplexing is not allowed in system bus.                                                            |

[In microprocessor-based systems, each bit of information (data/address/control signal) is send through a separate conducting line. Due to practical limitations, the manufacturers of microprocessors may provide multiplexed pins, i.e., one pin is used for more than one purpose. This leads to multiplexed CPU bus. For example in 8085 processor the low byte of address and data are send through same pins but at different timings. But when the system is formed, the multiplexed bus lines should be demultiplexed by using latches, ports, transceivers, etc. The demultiplexed bus lines are called system bus. In a system, separate conducting line will be provided for each bit of data, address and control signals.]

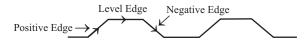

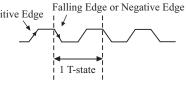

*Clock* : A clock is a square wave, which is used to synchronize various devices in the microprocessor and in the system. Every microprocessor system requires a clock for its functioning. The time taken for the microprocessor and the system to execute an instruction or program are measured only in terms of the time period of its clock.

The clock has three edges. They are: rising edge (positive edge), level

edge and falling edge (negative edge). The devices are made sensitive to any one of the edge for better functioning i.e., the device will recognize the clock only when the edge is asserted or arrived).

*Tristate Logic* : Almost all the devices used in the microprocessor-based system uses tristate logic. In devices with tristate logic, three logic levels will be available. They are **high** state, **low** state and **high impedance** state.

The **high** and **low** are normal logic levels for data, address or control signals. The **high impedance** state is electrical open circuit condition. The **high impedance** state is provided to keep the device electrically isolated from the system. The tristate devices will normally remain in **high impedance** state and their pins are physically connected in the system bus but electrically isolated. In **high impedance** state, they cannot receive or send any signal or information. These devices are provided with chip enable/ chip select pins. When the signal at this pin is asserted to the right level, they come out from **high impedance** state to normal levels.

#### **1.2 EVOLUTION OF MICROPROCESSOR**

History shows us that the ancient Babylonians first began using the abacus (a primitive calculator made of beads) in about 500 BC. This simple calculating machine eventually sparked human mind into the development of calculating machinery that uses gears and wheels (Blaise Pascal in 1642). The giant computing machines of the 1940s and 1950s were constructed with relays and vacuum tubes. Next, the transistor and solid-state electronics were used to build the mighty computers of the 1960s. Finally, the advent of the Integrated Circuit (IC) led to the development of the microprocessor and microprocessor-based computer system.

In 1971, INTEL corporation released the world's first microprocessor - the INTEL 4004, a 4-bit microprocessor. It addresses 4096 memory locations of word size 4-bit. The instruction set consists of 45 different instructions. It is a monolithic IC employing large scale integration in PMOS Technology. The INTEL 4004 was soon followed by a variety of microprocessors, with most of the major semiconductor manufacturers producing one or more types.

#### **First Generation Microprocessors**

The microprocessors introduced between 1971 and 1973 were the first generation processors. They were designed using PMOS technology. This technology provided low cost, slow speed and low output currents and was not compatible with TTL (Transistor Transistor Logic) levels.

The first generation processors require a lot of additional support of ICs to form a system. They may require as high as 30 ICs to form a system. The 4-bit processors are provided with only 16 pins, but 8-bit and 16-bit processors are provided with 40 pins. Due to limitations of pins, the signals are multiplexed. A list of first generation microprocessors are given below:

| • | INTEL 4004                 | )                 |

|---|----------------------------|-------------------|

| • | INTEL 4040                 |                   |

| • | FAIR CHILD PPS - 25        |                   |

| • | NATIONAL IMP - 4           | 4-bit processors  |

| • | ROCKWELL PPP - 4           | Ĩ                 |

| • | MICRO SYSTEMS INTL. MC - 1 |                   |

| • | INTEL 8008                 | )                 |

| • | NATIONAL IMP - 8           | )                 |

| • | ROCKWELL PPS - 8           | 0 hit massage     |

| • | AMI 7200                   | 8-bit processors  |

| • | MOSTEK 5065                | J                 |

| • | NATIONAL IMP/16            | ]                 |

| • | NATIONAL PACE              | 16-bit processors |

|   |                            | J                 |

#### **Second Generation Microprocessors**

The second generation microprocessors appeared in 1973 and were manufactured in NMOS Technology. The NMOS technology offers faster speed and higher density than PMOS and it is TTL compatible. Some of the second generation processors are given below:

INTEL 8080

•

- INTEL 8085 8-bit processors

- FAIRCHILD F 8

| ( | MOTOROLA M6800             | )      |                   |

|---|----------------------------|--------|-------------------|

| ( | MOTOROLA M6809             |        |                   |

|   | NATIONAL CMP -8            |        |                   |

|   | RCA COSMAC                 | {      | 8-bit processors  |

|   | MOS TECH. 6500             |        |                   |

|   | SIGNETICS 2650             |        |                   |

|   | ZILOG Z80                  | ן<br>ו |                   |

|   | INTERSIL 6100              | ł      | 12-bit processors |

| • | TOSHIBA TLCS - 12          | J      |                   |

|   | TI TMS 9900                | )      |                   |

|   | DFC - WD MCP - 1600        |        | 4 < 1 *           |

|   | GENERAL INSTRUMENT CP 1600 | Ì      | 16-bit processors |

|   | DATA GENERAL μN601         |        |                   |

#### Characteristics of second generation microprocessors

- Larger chip size ( $170 \times 200$  mils). [1mil =  $10^{-3}$ inch] •

- 40 pins.

- More numbers of on-chip decoded timing signals.

- The ability to address large memory spaces.

- The ability to address more IO ports.

- Faster operation.

- More powerful instruction set.

- A greater number of levels of subroutine nesting.

- Better interrupt handling capabilities.

#### Third Generation Microprocessors

After 1978, the third generation microprocessors were introduced. These are 16-bit processors and designed using HMOS (High density MOS) Technology. Some of the third generation microprocessors are given below:

INTEL 8086 •

**INTEL 8088**

- **INTEL 80286**

- **ZILOG Z8000** NATIONAL NS 16016

INTEL 80186 •

•

- MOTOROLA 68000 • MOTOROLA 68010

- **TEXAS INSTRUMENTS TMS 99000** •

The HMOS technology offers better Speed Power Product (SPP) and higher packing density than NMOS.

Speed Power Product = Speed  $\times$  Power

- = Nanosecond × Milliwatt

- = Picojoules

- Speed Power Product of HMOS is four times better than NMOS. SPP of NMOS = 4 picojoules (pJ) SPP of HMOS = 1 picojoules (pJ)

•

•

•

Circuit densities provided by HMOS are approximately twice than those of NMOS. Packing density of NMOS = 1852.5 gates/mm<sup>2</sup> Packing density of HMOS = 4128 gates/mm<sup>2</sup> (1 mm =  $10^{-6}$  meter)

1.4

#### Characteristics of third generation microprocessors

- Provided with 40/48/64 pins.

- High speed and very strong processing capability.

- Easier to program.

- Allow for dynamically relocatable programs.

- Size of internal registers are 8/16/32 bits.

- The processor has multiply/divide arithmetic hardware.

- Physical memory space is from 1 to 16 Mega bytes.

- The processor has segmented addresses and virtual memory features.

- More powerful interrupt handling capabilities.

- Flexible IO port addressing.

- Different modes of operations (e.g., user and supervisor modes of M68000).

#### **Fourth Generation Microprocessors**

The fourth generation microprocessors were introduced in the year 1980. The fourth generation processors are 32-bit processors and are fabricated using the low-power version of the HMOS technology called the HCMOS. These 32-bit microprocessors have increased sophistications that compete strongly with the mainframes. Some of the fourth generation microprocessors are given below:

- INTEL 80386

MOTOROLA M68020

MOTOROLA MC88100

- INTEL 80486 BELLMAC 32

- NATIONAL NS16032

MOTOROLA M68030

#### Characteristics of fourth generation microprocessors

- Physical memory space of 2<sup>24</sup> bytes = 16 Mb (Mega bytes).

- Virtual memory space of 2<sup>40</sup> bytes = 1 Tb (Tera bytes).

- Floating point hardware is incorporated.

- Supports increased number of addressing modes.

#### **Fifth Generation Microprocessors**

In microprocessor technology, INTEL has taken a leading edge and is developing more and more new processors. The INTEL **pentium** processor released in the year 1993 is considered as a fifth generation processor. The pentium is 32-bit processor with 64-bit data bus and available in wide range of clock speeds from 60 MHz to 3.2 GHz. With the improvement in semiconductor technology, the processing speed of microprocessors have been increased tremendously. The 8085 released in the year 1976 executes 0.5 Million Instructions Per Second (0.5 MIPS). The 80486 executes 54 Million Instructions Per Second. The pentium is optimized to execute two instructions in one clock period. Therefore, a pentium processor working at 1GHz clock can execute 2000 Million Instructions Per Second (2000 MIPS). The various processors released by INTEL are listed in Appendix-III.

#### **Applications of Microprocessors of Different Generations**

#### **First generation processor**

- Calculators

- Game machines

- Home appliances

- Accounting systems

- Intelligent instrumentation

- Low and special purpose applications

#### 1.6

Chapter 1 Introduction to Microprocessor

#### Second generation processors

- Complex industrial controllers

- Communication perprocessors

- Process control systems

- Data acquisition systems

#### Third generation processors

- Business and data processing applications

- Sophisticated real time control

- Advanced communications

- Distributed processing networks

#### Fourth generation processors

- General purpose computing in applications requiring mainframe type computing power.

- Multiuser, multifunction environments.

- Office information equipment.

#### **1.3 BASIC FUNCTIONAL BLOCKS OF A MICROPROCESSOR**

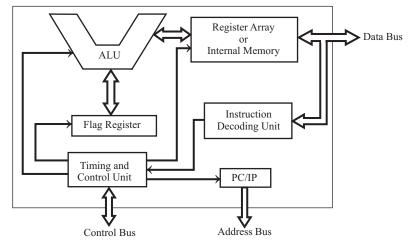

The microprocessor is a programmable IC which is capable of performing arithmetic and logical operations. The basic functional block diagram of a microprocessor is shown in Fig. 1.1.

The basic functional blocks of a microprocessor are ALU, flag register, register array, **P**rogram Counter (PC)/Instruction Pointer (IP), instruction decoding unit, timing and control unit.

Fig. 1.1 : Block diagram showing basic functional blocks of a microprocessor.

ALU is the computational unit of the microprocessor which performs arithmetic and logical operations on binary data. The various conditions of the result are stored as status bits called flags in the flag register. For example, consider a sign flag, one of the bit position of flag register is called sign flag and it is used to store the status of sign of the result of ALU operation (output data of ALU). If the result is negative, then "1" is stored in the sign flag and if the result is positive, then "0" is stored in the sign flag.

- Instrumentation

- Intelligent terminals

- Military applications

The register array is the internal storage device and so it is also called *internal memory*. The input data for ALU, the output data of ALU (result of computations) and any other binary information needed for processing are stored in the register array.

For any microprocessor, there will be a set of instructions given by the manufacturer of the microprocessor. For doing any useful work with the microprocessor, we have to write a program using these instructions, and store them in a memory device external to the microprocessor.

The program counter generates the address of the instructions to be fetched from the memory and send through address bus to the memory. The memory will send the instruction codes and data through the data bus. The instruction codes are decoded by the decoding unit and send information to timing and control unit. The data is stored in the register array for processing by ALU.

The control unit will generate the necessary control signals for internal and external operations of the microprocessor.

#### 1.4 MICROPROCESSOR-BASED SYSTEM (ORGANIZATION OF MICROCOMPUTER)

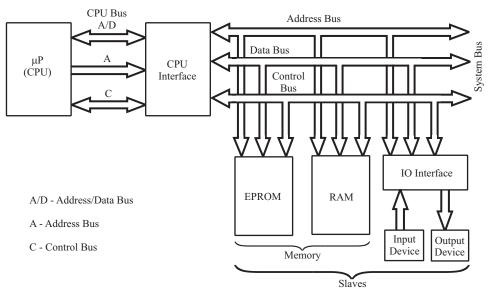

The microprocessor is a semiconductor device (or Integrated Circuit) manufactured by the VLSI (Very Large Scale Integration) technique. It includes the ALU, register arrays and control circuit on a single chip. To perform a function or useful task, we have to form a system by using microprocessor as a CPU (Central Processing Unit) and interfacing memory, input and output devices to it. A system designed using a microprocessor as its CPU is called a *microcomputer or single board microcomputer*. The microprocessor-based system consists of microprocessor as CPU, semiconductor memories like EPROM and RAM, input device, output device and interfacing devices. The memories, input device, output device and interfacing devices are called *peripherals*.

The commonly used EPROM and static RAM in microcomputers are given below:

| <b>EPROM</b>      | Static RAM           |

|-------------------|----------------------|

| INTEL 2708 (1 kb) | MOTOROLA 6208 (1 kb) |

| INTEL 2716 (2 kb) | MOTOROLA 6216 (2 kb) |

| INTEL 2732 (4 kb) | MOTOROLA 6232 (4 kb) |

| INTEL 2764 (8 kb) | MOTOROLA 6264 (8 kb) |

|                   |                      |

*Note* : *kb* refer to Kilo bytes.

The popular input devices are keyboard, floppy disk, etc., and the output devices are printer, LED/LCD displays, CRT monitor, etc.

The block diagram of microprocessor-based system (organization of microcomputer) is shown in Fig. 1.2. In this system, the microprocessor is the master and all other peripherals are slaves. The master controls all the peripherals and initiates all operations.

The buses are group of lines that carry data, addresses or control signals. The CPU bus has multiplexed lines, i.e., the same line is used to carry different signals. The CPU interface is provided to demultiplex the multiplexed lines, to generate chip select signals and additional control signals. The system bus has separate lines for each signal.

Chapter 1 Introduction to Microprocessor

Fig. 1.2 : Microprocessor-based system (organization of microcomputer).

All the slaves in the system are connected to the same system bus. At any time instant communication takes place between the master and one of the slaves. All the slaves have tristate logic and hence normally remains in **high impedance** state. The processor selects a slave by sending an address. When a slave is selected, it comes to the normal logic and communicates with the processor.

The EPROM memory is used to store permanent programs and data. The RAM memory is used to store temporary programs and data. The input device is used to enter the program, data and to operate the system. The output device is also used for examining the results. Since the speed of IO devices does not match with the speed of microprocessor, an interface device is provided between system bus and IO devices. Generally, IO devices are slow devices.

The work done by the processor can be classified into the following three groups :

- 1. Work done internal to the processor.

- 2. Work done external to the processor.

- 3. Operations initiated by the slaves or peripherals.

The work done internal to the processor are addition, subtraction, logical operations, data transfer within registers, etc. The work done external to the processor are reading/writing the memory, and reading/writing the IO devices or the peripherals. If the peripheral requires the attention of the master, then it can interrupt the master and initiate an operation.

The microprocessor is the master, which controls all the activities of the system. To perform a specific job or task, the microprocessor has to execute a program stored in memory. The program consists of a set of instructions stored in consecutive memory location. In order to execute the program, the microprocessor issues address and control signals, to fetch the instruction and data from memory one by one. After fetching each instruction it decodes the instruction and carries out the task specified by the instruction.

1.8

#### **1.5 CONCEPT OF MULTIPLEXING IN MICROPROCESSOR**

Multiplexing is transferring different information at different well-defined times through same lines. A group of such lines are called multiplexed bus. The result of multiplexing is that fewer pins are required for microprocessors to communicate with the outside world.

Due to the pin number limitations, most microprocessors cannot provide simultaneously similar lines (such as address, data, status signals, etc.). Hence, multiplexing of one or more of these buses is performed. Most often data lines are multiplexed with some or all address lines to form an address/ data bus. (For example, in 8085, the lower 8 address lines are multiplexed with data lines.) The status signals emitted by the microprocessor are sometimes multiplexed either with the data lines (as done in INTEL 8080A) or with some of the address lines (as done in the INTEL 8086).

Whenever multiplexing is used, the CPU interface of the system must include the necessary hardware to demultiplex those lines to produce the separate address, data and control buses required for the system. Demultiplexing of a multiplexed bus can be handled either at the CPU interface or locally at appropriate points in the system. Besides a slower system operation, a multiplexed bus also results in additional interface hardware requirements.

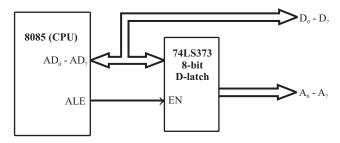

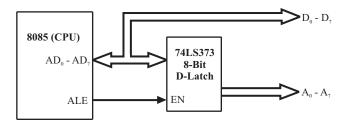

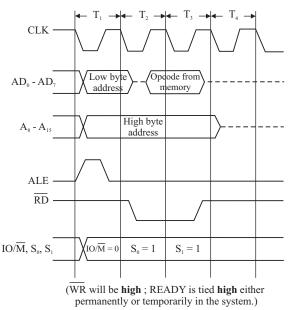

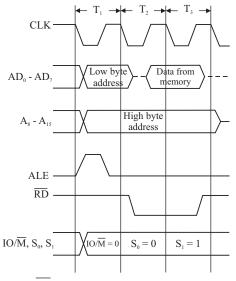

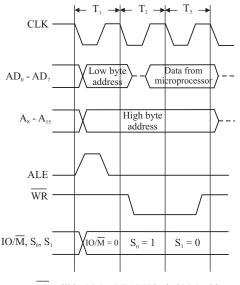

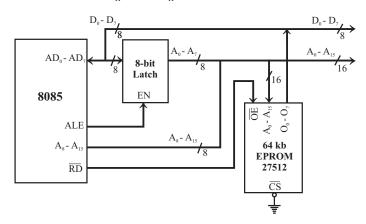

#### Demultiplexing of Address/Data Lines in 8085 Processor

In order to demultiplex the address/data lines (of the processor), the processor provides a signal called ALE (Address Latch Enable). The ALE is asserted **high** and then **low** by the processor at the beginning of every machine cycle. At the same time the low byte address is given out through  $AD_0 - AD_7$  lines. The demultiplexing of address/data lines using 8-bit D-latch 74LS373 is shown in Fig. 1.3.

The ALE is connected to the **En**able Pin (EN) of an external 8-bit latch. When ALE is asserted **high** and then **low**, the addresses are latched into the output lines of the latch. It holds the low byte of the address until the next machine cycle. After latching the address, the  $AD_0 - AD_7$  lines are free for data transfer. The first T-state of every machine cycle is used for address latching in 8085 and the remaining T states are used for reading or writing operation.

Fig. 1.3 : Demultiplexing of address and data lines in an 8085 processor.

#### 1.6 MICRO, MINI AND LARGE COMPUTERS

The computers are broadly classified into three categories : Main frame, Mini and Microcomputers.

In today's technology, the distinction between these categories are fast vanishing. The microcomputers have superceded the performance of minicomputers and now they are competing with mainframes.

#### Mainframes (Large Computers)

The largest and most powerful computers are called mainframes. Mainframe computers may occupy an entire room. They are designed to work at very high speed with large data words and have massive amounts of memory. Computers of this type are used for military defence control, business data processing and for creating computer graphics displays for science fiction movies. Examples of this type of computers are IBM 4381, Honeywell DPS8 and CRAY X-MP/48.

#### Minicomputers

The scaled-down versions of mainframe computers are often called minicomputers. The main unit of a minicomputer usually fits in a single rack or box. A minicomputer runs more slowly, work directly with smaller data words and does not have as much memory as a mainframe. Computers of this type are used for business data processing, industrial control and scientific research. Examples of this type of computers are the Digital Equipment Corp.-VAX 11/730, the Data General-MV/800011 and HCL's-MAGNUM.

The CPU of the minicomputers have more than one microprocessor and their coprocessors.

#### Microcomputers

As the name implies, microcomputers are small computers. They range from small controllers that work directly with 4-bit words and can address a few thousand bytes of memory to large units that work directly with 64-bit words and can address millions or billions of bytes of memory.

Some of the more powerful microcomputers have all or most of the features of earlier minicomputers. Therefore, it has become very hard to draw a sharp line between these two types.

One distinguishing feature of a microcomputer is that the CPU is usually a single microprocessor. The examples of microcomputer are IBM PC/80, AT286, AT386, AT486, etc.

#### Comparison of Large, Mini and Micro Computers

The computers can be compared based on the following features:

Speed of execution

Size of data

Memory capacity it can support

Types of data

IO devices and peripheral support devices

Applications

They are further listed in Table-1.1.

#### Advantages of Microprocessor-Based System

- 1. Computational or processing speed is high.

- 2. Intelligence has been brought to systems.

- 3. Automation of industrial processes and office administration.

- 4. Since the devices are programmable, there is flexibility to alter the system by changing the software alone.

- 5. Less number of components, compact in size and less cost. It is also more reliable.

- 6. Both operation and maintenance are easier.

1.10

|    | Features                                 | Mainframe / Large computers                                                                                                                                                        | Minicomputers                                                                                                               | Microcomputers                                                                                                                                                       |

|----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ·  | 1. Speed of execution                    | Executes 100 to 3000 Million<br>Instructions Per Second (MIPS).                                                                                                                    | Executes up to 100 Million<br>Instructions Per Second (MIPS).                                                               | Ranges from 0.5 MIPS<br>(8085) to 54 MIPS (80486)                                                                                                                    |

| ъ, | Size of data                             | 64 or 128 bits.                                                                                                                                                                    | 32 or 64 bits.                                                                                                              | 4 bits to 64 bits.                                                                                                                                                   |

| ю. | 3. Memory capacity                       | Thousands of Gb.                                                                                                                                                                   | In the range of few Gb.                                                                                                     | Ranges from kb to Gb<br>(kb-kilo-byte, Gb-Giga-byte)                                                                                                                 |

| 4  | 4. Types of data                         | All types (Binary, ASCII, decimal,<br>floating point data, complex<br>numbers, etc.).                                                                                              | Same as main frame.<br>8085 - operates only on binary                                                                       | Depends on the micro-<br>processor used as CPU.<br>8086 - Binary, BCD, ASCII.                                                                                        |

| 5. | 5. IO devices and<br>support peripherals | All types of IO devices and<br>peripheral devices will be<br>interfaced in the system.                                                                                             | Common input devices are<br>tapes, floppies, etc. Types<br>of output device depends on<br>the user needs.                   | Common IO devices are<br>keyboard, floppies and<br>output devices are CRT and<br>printer. The support<br>peripheral device depends<br>on applications of the system. |

| 9. | 6. Applications                          | Scientific calculation, weather data<br>processing, large business data<br>processing, real time applications,<br>multiuser business systems,<br>instructional system in colleges. | Multiuser business systems,<br>word processing,<br>process control, office<br>automation, hospital patient<br>care systems. | Personal computing,<br>calculators, small business<br>systems, control applications,<br>instrumentation systems.                                                     |

TABLE - 1.1 : COMPARISON OF MAINFRAMES, MINICOMPUTERS AND MICROCOMPUTERS

Microprocessor (8085) And Its Applications

1.11

#### 1.12

#### **Disadvantages of Microprocessor-Based System**

- 1. It has limitations on the size of data.

- 2. The applications are limited by the physical address space.

- 3. The analog signals cannot be processed directly and digitizing the analog signals introduces errors.

- 4. The speed of execution is slow and so real time applications are not possible.

- 5. Most of the microprocessors do not support floating point operations.

#### Applications of Microprocessor-Based Systems

Typical applications for different systems, categorized by the data size of ALU of the processor, include the following :

#### 4-bit systems

- Accounting systems

- Home Appliances

- Calculators

#### 8-bit systems

- Control systems

- Intelligent terminals and instruments

- Process control systems

#### 16-bit systems

- Data acquisition system

- Intelligent terminals

- Automatic testing systems

- Game Machines

- Intelligent Instrumentation

- Terminals (simple)

- Point of sale terminals

- Traffic controllers

- Communication preprocessors (data concentrators)

- Numerical control

- Process control

- Supervisory control (gas, power, water distribution) and many more applications

#### 1.7 INTEL 8085

The INTEL 8085 is an 8-bit microprocessor released in the year 1976. The 8085 is designed using NMOS technology and now it is manufactured using HMOS technology and it contains approximately 6500 transistors. The 8085 is packed in a 40-pin DIP (**D**ual In-line **P**ackage) and requires a single 5-volt supply.

The 8085 has an internal clock oscillator. It generates a clock signal internally and divides by two and then uses as internal clock. This internal clock is also given out through CLK pin for the clock requirement of peripheral devices.

The NMOS 8085 is available in two versions : 8085A and 8085A-2 with maximum internal clock frequency of 3.03 MHz and 5MHz, respectively. The enhanced version of 8085 is designed with HMOS transistors. It is available in three versions: 8085AH, 8085AH-2 and 8085AH-1 with maximum internal clock of 3MHz, 5MHz and 6MHz, respectively.

The basic data size of 8085 is 8-bit. Therefore, the memory word size of the memories interfaced with 8085 processor is also 8-bit or byte. The 8085 uses a 16-bit address to access memory and hence it can address upto  $2^{16} = 65,536_{10} = 64$  k memory locations. Since one-byte of

information can be stored in one memory location, the maximum memory capacity of 8085-based system is 64 kilo bytes. For accessing IO-mapped devices, the 8085 uses a separate 8-bit address and so it can generate  $2^8 = 256_{10}$  IO addresses.

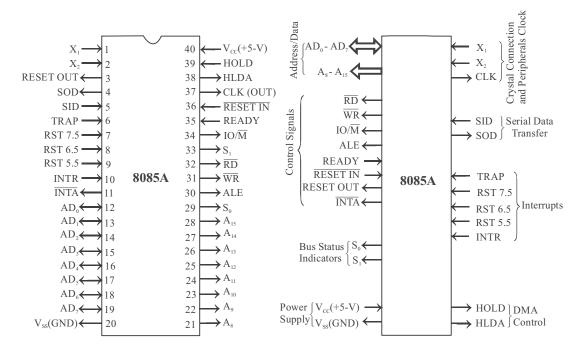

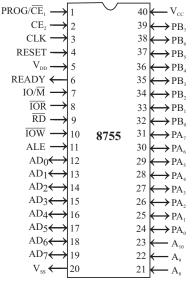

The pin configuration of 8085 is shown in Fig. 1.4. The signals of 8085 are listed in Table-1.2. The 8085 has 8 pins  $AD_0$  to  $AD_7$  for data transfer, which are multiplexed with low byte of address. The 8085 provides a signal ALE (Address Latch Enable) to demultiplex the low byte address and data using an external latch. The demultiplexing of address and data lines in 8085 is shown in Fig. 1.3 in Section 1.5.

Fig. 1.4: 8085 microprocessor signals and pin assignment.

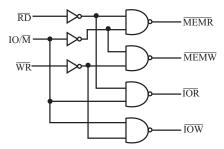

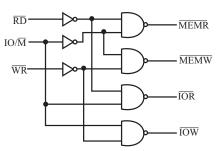

During memory access, the 16-bit memory address are output on  $AD_0$  to  $AD_7$  and  $A_8$  to  $A_{15}$  lines. During IO access of IO-mapped devices, the 8-bit IO address are output on both  $AD_0$  to  $AD_7$  and  $A_8$  to  $A_{15}$  lines. The 8085 processor differentiates the memory and IO address using the signal IO/ $\overline{M}$ . When the processor output gives a memory address, the IO/ $\overline{M}$  is asserted **low** and when the processor output gives an IO address, the IO/ $\overline{M}$  is asserted **high**.

The  $\overline{\text{RD}}$  signal is asserted **low** by the processor during a memory or IO read operation. The  $\overline{\text{WR}}$  signal is asserted **low** by the processor during a memory or IO write operation. The S<sub>0</sub> and S<sub>1</sub> are bus status indicators. The output signals on these lines during various bus activity (or machine cycles) are listed in Table-1.3.

1.14

| Pin name                         | Description                         | Туре                    |

|----------------------------------|-------------------------------------|-------------------------|

| $AD_0 - AD_7$                    | Address/Data                        | Bidirectional, Tristate |

| A <sub>8</sub> - A <sub>15</sub> | Address                             | Output, Tristate        |

| ALE                              | Address latch enable                | Output, Tristate        |

| RD                               | Read control                        | Output, Tristate        |

| WR                               | Write control                       | Output, Tristate        |

| IO/M                             | IO or memory indicator              | Output, Tristate        |

| S <sub>0</sub> , S <sub>1</sub>  | Bus state indicators                | Output                  |

| READY                            | Wait state request                  | Input                   |

| SID                              | Serial input data                   | Input                   |

| SOD                              | Serial output data                  | Output                  |

| HOLD                             | Hold request                        | Input                   |

| HLDA                             | Hold acknowledge                    | Output                  |

| INTR                             | Interrupt request                   | Input                   |

| TRAP                             | Nonmaskable interrupt request       | Input                   |

| RST 5.5                          | Hardware vectored interrupt request | Input                   |

| RST 6.5                          | Hardware vectored interrupt request | Input                   |

| RST 7.5                          | Hardware vectored interrupt request | Input                   |

| INTA                             | Interrupt acknowledge               | Output                  |

| RESET IN                         | System reset                        | Input                   |

| RESET OUT                        | Peripherals reset                   | Output                  |

| X <sub>1</sub> , X <sub>2</sub>  | Crystal or RC connection            | Input                   |

| CLK (OUT)                        | Clock signal                        | Output                  |

| V <sub>cc</sub>                  | +5-V                                | Power supply            |

| V <sub>ss</sub>                  | Ground                              | Power supply            |

#### TABLE - 1.2 : 8085 SIGNAL DESCRIPTION SUMMARY

Note : An overbar on the signal, indicates that it is active low (i.e., the signal is normally high and when the signal is activated it is low).

| IO/M | S <sub>1</sub> | S <sub>0</sub> | Operation performed by 8085 |

|------|----------------|----------------|-----------------------------|

| 0    | 0              | 1              | Memory write                |

| 0    | 1              | 0              | Memory read                 |

| 1    | 0              | 1              | IO write                    |

| 1    | 1              | 0              | IO read                     |

| 0    | 1              | 1              | Opcode fetch                |

| 1    | 1              | 1              | Interrupt acknowledge       |

#### TABLE - 1.3 : BUS STATUS SIGNALS

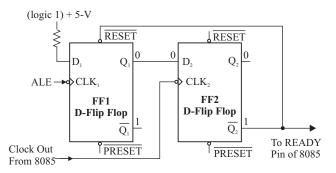

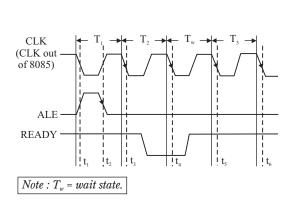

The READY is an input signal that can be used by slow peripherals to get extra time in order to communicate with 8085. The 8085 will work only when READY is tied to logic **high**. Whenever READY is tied to logic **low**, the 8085 will enter a wait state. When the system has slow peripheral devices, additional hardware is provided in the system to make the READY input **low** during the required extra time while executing a machine cycle, so that the processor can remain in wait state during this extra time.

The HOLD and HLDA signals are used for the **D**irect **M**emory **A**ccess (DMA) type of data transfer. This type of data transfers are achieved by employing a DMA controller in the system. When DMA is required, the DMA controller will place a **high** signal on the HOLD pin of 8085. When HOLD input is asserted **high**, the processor will enter a wait state and drive all its tristate pins to **high impedance** state and send an acknowledge signal to DMA controller through HLDA pin. Upon receiving the acknowledge signal, the DMA controller will take control of the bus and perform DMA transfer, and at the end it asserts HOLD signal **low**. When HOLD is asserted **low**, the processor will resume its execution.

The 8085 has five interrupt pins. The order of priority of the interrupts is TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR. The interrupts TRAP, RST 7.5, RST 6.5 and RST 5.5 are hardware vectored interrupt and are enabled by appropriate signals at the appropriate pins of 8085. When a vectored interrupt is enabled and if it is accepted, then the program execution branches to vector addresses specified by INTEL. The interrupts RST 7.5, RST 6.5 and RST 5.5 are maskable interrupts by software.

The INTR is enabled by appropriate signal at its pin. In order to service INTR, one of the eight opcodes (RST 0 to RST 7) has to be provided on the  $AD_0 - AD_7$  bus by external logic. The 8085 then executes this instruction and vectors to the appropriate address to service the interrupt. The vector address for an interrupt RST n is given by  $(08 \times n)_{\rm H}$ . The vector addresses of the interrupts of 8085 are listed in Table-1.4. (The interrupt TRAP is RST 4.5.)

| Interrupt | Vector address    | Interrupt | Vector address    |

|-----------|-------------------|-----------|-------------------|

| RST 0     | 0000 <sub>H</sub> | RST 5     | 0028 <sub>H</sub> |

| RST 1     | 0008 <sub>H</sub> | RST 5.5   | 002C <sub>H</sub> |

| RST 2     | 0010 <sub>H</sub> | RST 6     | 0030 <sub>H</sub> |

| RST 3     | 0018 <sub>н</sub> | RST 6.5   | 0034 <sub>H</sub> |

| RST 4     | 0020 <sub>H</sub> | RST 7     | 0038 <sub>н</sub> |

| TRAP      | 0024 <sub>H</sub> | RST 7.5   | 003C <sub>H</sub> |

#### **TABLE - 1.4 : VECTOR ADDRESSES OF INTERRUPTS**

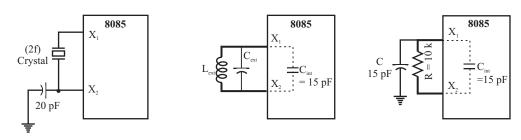

The 8085 has the clock generation circuit on the chip but an external quartz crystal or LC circuit or RC circuit should be connected at the pins  $X_1$  and  $X_2$ . The frequency at  $X_1$  and  $X_2$  is divided by two internally, and are used as internal clock. The frequency of output clock signal at CLK(OUT) pin is same as that of internal clock.

The RESET IN is the system reset input signal and it is used to bring the processor to a known state. For proper reset, the RESET IN pin should be held **low** for at least three clock periods. When RESET IN pin is asserted **low**, the program counter, instruction register, interrupt mask bits and all internal registers are cleared or resetted. Also, the RESET OUT signal is asserted **high** to clear or reset all the peripheral devices in the system. After a reset, the content of program counter will be  $0000_{\mu}$  and so the processor will start executing the program stored at  $0000_{\mu}$ .

The pins SID and SOD can be used for serial data communication between 8085 and any serial device under software control.

#### Driving X<sub>1</sub> and X<sub>2</sub> Inputs

The  $X_1$  and  $X_2$  pins of 8085 processor are provided to connect an external quartz crystal or LC circuit. It can also be driven by RC circuit or an external clock source. This connection is necessary for the internal oscillator to generate the clock signal for the processor. An oscillator consists of an amplifier and a feedback circuit. The feedback circuit of an oscillator can be RC type, LC type or quartz crystal (a quartz crystal is electrically equivalent to RLC circuit). The feedback circuit also decides the frequency of the signal generated by the oscillator.

In 8085 processor, the oscillator circuit is provided internally except the feedback circuit. This feature, facilitates the system designer to choose his own frequency for clock signals. But this frequency should not exceed the maximum clock frequency specified by the manufacturer. Another reason for keeping feedback circuit external to the processor is that the high Q circuits (quartz crystal or large values of L) cannot be fabricated by IC technology.

In 8085, the frequency generated by the oscillator circuit will be double than that of internal clock frequency. (The maximum clock frequencies specified by the manufacturer are internal clock frequencies.) In other words, the frequency at  $X_1 - X_2$  pins of 8085 is divided by two, internally. This means that in order to obtain an internal clock of 3.03MHz, a clock source of 6.06 MHz must be connected to  $X_1 - X_2$ . (Crystal/LC/RC should be designed to double the internal frequency.)

The quartz crystals are the best choice for connecting at  $X_1 - X_2$ , because they are less expensive, highly stable, have large Q, occupy very small space and frequencies do not drift with ageing. For crystals with less than 4MHz, a capacitor of 20 pF should be connected between  $X_2$  and the ground to ensure the starting up of the crystal at the right frequency.

When LC circuit is used, the value of  $L_{ext}$  and  $C_{ext}$  can be chosen using the formula,

$$f = \frac{I}{2\pi L_{ext} (C_{ext} + C_{int})}$$

To minimize the variations in frequency, it is recommended that the value for  $C_{ext}$  should be twice than that of  $C_{int}$  or 30 pF. The use of LC circuit is not recommended for external frequencies higher than 5 MHz.

1.16

*Fig. 1.5a* : *Capacitor required for crystals* with frequency less than 4 Mhz.

Fig. 1.5b : LC tuned circuit clock driver.

Fig. 1.5c : RC circuit clock source.

Fig. 1.5 : Clock driver circuits for an 8085.

An RC circuit may also be used as the clock source for the 8085A if an accurate clock frequency is of no concern. Its advantage is its low component cost. The values shown in Fig. 1.5 are for generating an approximate external frequency of 3 MHz. Note that the frequencies higher or lower than 3 MHz should not be attempted on this circuit.

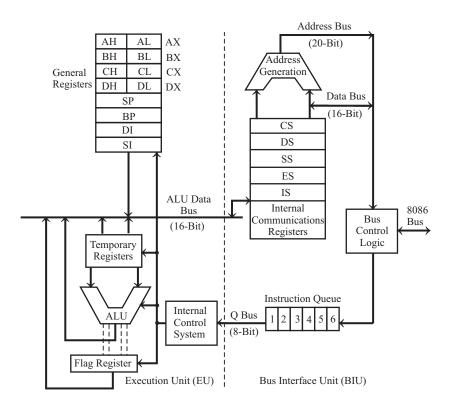

#### Architecture of INTEL 8085

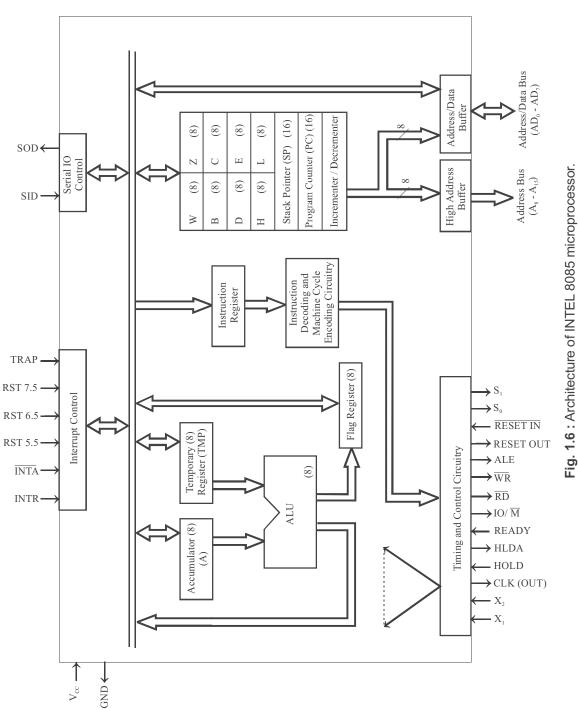

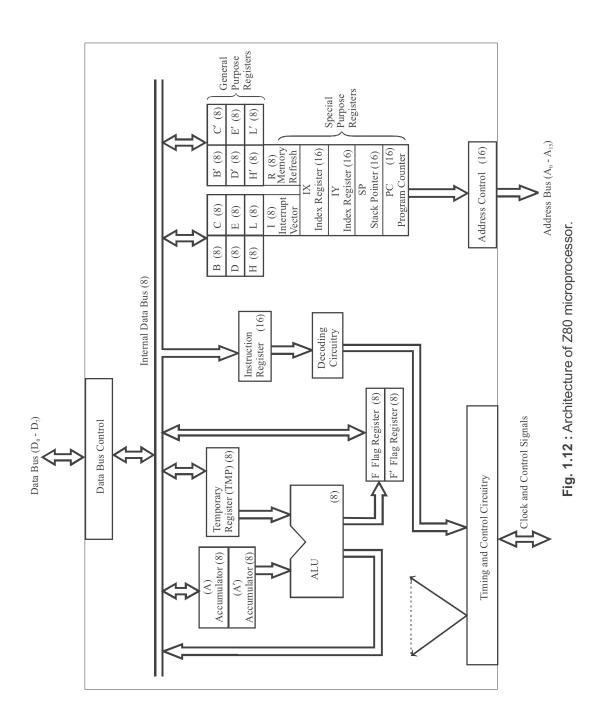

The architecture of 8085 is shown in Fig. 1.6. The 8085 includes the ALU, timing and control unit, instruction register and decoder, register array, interrupt control and serial IO control.

The ALU performs the arithmetic and logical operations. The operations performed by ALU of 8085 are addition, subtraction, increment, decrement, logical AND, OR, EXCLUSIVE-OR, compare, complement and left/right shift. The accumulator and temporary register are used to hold the data during an arithmetic/logical operation. After an operation, the result is stored in the accumulator and the flags are set or reset according to the result of the operation. The accumulator and flag register together are called Program Status Word (PSW).

There are five flags in 8085, they are: **Sign Flag (SF)**, **Zero Flag (ZF)**, **Auxiliary Carry Flag (AF)**, **Parity Flag (PF) and Carry Flag (CF)**. The bit positions reserved for these flags in the flag register are shown in Fig. 1.7.

After an ALU operation if the most significant bit of the result is 1, the sign flag is set. The zero flag is set if the ALU operation results in zero and it is reset if the result is nonzero. In an arithmetic operation, when a carry is generated by the lower nibble, the auxiliary carry flag is set. After an arithmetic or logical operation if the result has an even number of 1's the parity flag is set, otherwise it is reset.

If an arithmetic operation results in a carry, the carry flag is set, otherwise it is reset. Among the five flags, the AF Flag is used internally for BCD arithmetic and other four flags can be used by the programmer to check the conditions of the result of an operation.

Chapter 1 Introduction to Microprocessor

1.18

| $B_7$ | $B_6$ | $B_5$ | $B_4$ | B <sub>3</sub> | $B_2$ | $\mathbf{B}_{1}$ | $B_0$ |

|-------|-------|-------|-------|----------------|-------|------------------|-------|

| SF    | ZF    |       | AF    |                | PF    |                  | CF    |

Fig. 1.7 : Bit positions of various flags in the flag register of 8085.

The timing and control unit synchronizes all the microprocessor operations with the clock, and generates the control signals necessary for communication between the microprocessor and peripherals.

When an instruction is fetched from memory, it is placed in instruction register. It is then decoded and encoded into various machine cycles. Apart from Accumulator (A-register), there are six general purpose programmable registers B, C, D, E, H and L. They can be used as 8-bit registers or paired to store 16-bit data. The allowed pairs are BC, DE and HL. The temporary registers TMP, W and Z cannot be used by the programmer.

The Stack Pointer (SP), holds the address of the stack top. The stack is a sequence of RAM memory locations defined by the programmer. The stack is used to save the content of registers during the execution of a program.

The **P**rogram **C**ounter (PC) keeps a track of program execution. To execute a program, the starting address of the program is loaded in program counter. The PC sends out an address to fetch a byte of instruction from memory and increment its content automatically. Hence, when a byte of instruction is fetched, the PC holds the address of the next byte of the instruction or next instruction.

#### Instruction Execution and Data Flow in 8085

The program instructions are stored in memory which is an external device. In order to execute a program in 8085, the starting address of the program should be loaded in program counter. The 8085 output is the content of program counter to address bus and asserts read control signal **low**. Also, the program counter is incremented.

The address and the read control signal enables the memory to output the content of memory location on the data bus. Now the content of data bus is the opcode of an instruction. The read control signal is made **high** by timing and control unit after a specified time. At the rising edge of read control signals, the opcode is latched into microprocessor internal bus and placed in instruction register.

The instruction decoding unit, decodes the instruction and provides information to timing and control unit to take further actions.

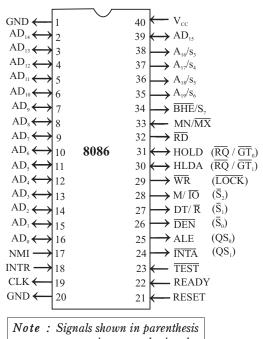

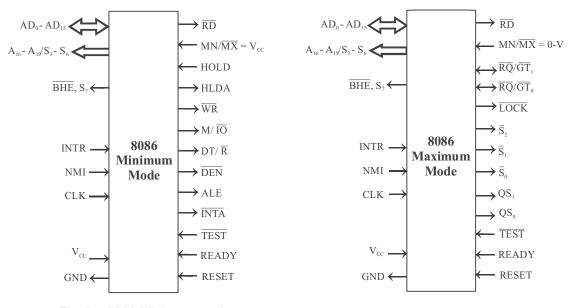

#### 1.8 INTEL 8086

INTEL 8086 is the first 16-bit processor released by INTEL in the year 1978. The 8086 is designed using the HMOS technology and now it is manufactured using HMOS III technology and contains approximately 29,000 transistors. The 8086 is packed in a 40-pin DIP and requires a single 5-volt supply.

The 8086 does not have internal clock circuit. The 8086 requires an external asymmetric clock source with 33% duty cycle. The 8284 clock generator is used to generate the required clock for 8086. The maximum internal clock of 8086 is 5 MHz. The other versions of 8086 with different clock rates are 8086-1, 8086-2 and 8086-4 with maximum internal clock frequency of 10 MHz, 8 MHz and 4 MHz respectively.

The 8086 uses a 20-bit address to access memory and hence it can directly address up to one mega-byte ( $2^{20} = 1$ Mega) of memory space. The one mega-byte (1Mb) of addressable memory space of 8086 is organized as two memory banks of 512 kilo bytes each (512 kb + 512 kb = 1Mb). The memory banks are called even (or lower) bank and odd (or upper) bank. The address line A<sub>0</sub> is used to select even bank and the control signal  $\overline{BHE}$  is used to select odd bank.

For accessing IO-mapped devices, the 8086 uses a separate 16-bit address, and so the 8086 can generate 64 k ( $2^{16}$ ) IO addresses. The signal M/IO is used to differentiate the memory and IO addresses. For memory address, the signal M/IO is asserted **high** and for IO address the signal M/IO is asserted **low** by the processor.

The 8086 can operate in two modes, and they are minimum mode and maximum mode. The mode is decided by a signal at  $MN/\overline{MX}$  pin. When the  $MN/\overline{MX}$  is tied **high**, it works in minimum mode and the system is called uniprocessor system. When  $MN/\overline{MX}$  is tied **low**, it works in maximum mode and the system is called multiprocessor system. Usually, the pin  $MN/\overline{MX}$  is permanently tied to **low** or **high** so that the 8086 system can work in any one of the two modes. The 8086 can work with 8087 coprocessor in maximum mode. In this mode, an external bus controller 8288 is required to generate bus control signals.

The 8086 has two families of processors. They are 8086 and 8088. The 8088 uses 8-bit data bus externally but 8086 uses 16-bit data bus externally. The 8086 can access memory in words but 8088 can access memory in bytes. The IBM designed its first **P**ersonal **C**omputer (PC) using INTEL 8088 microprocessor as CPU.

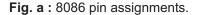

#### Pins and Signals of INTEL 8086

The 8086 pins and signals are shown in Fig. 1.8. The 8086 is a 40-pin IC and all the 8086 pins are TTL compatible. The signal assigned to pins 24 to 31 will be different for minimum and maximum mode of operation. The signal assigned to all other pins are common for minimum and maximum mode of operation.

are maximum mode signals.

Fig. c: 8086-Maximum mode.

Fig. 1.8: 8086 pin and signals.

1. 22

| Name                                                             | <b>Description</b> /Function  | Туре                    |

|------------------------------------------------------------------|-------------------------------|-------------------------|

| $AD_{15} - AD_{0}$                                               | Address/Data                  | Bidirectional, Tristate |

| A <sub>19</sub> /S <sub>6</sub> -A <sub>16</sub> /S <sub>3</sub> | Address/Status                | Output, Tristate        |

| BHE/S <sub>7</sub>                                               | Bus high enable/Status        | Output, Tristate        |

| MN/MX                                                            | Minimum/Maximum mode control  | Input                   |

| RD                                                               | Read control                  | Output, Tristate        |

| TEST                                                             | Wait on test control          | Input                   |

| READY                                                            | Wait on state control         | Input                   |

| RESET                                                            | System reset                  | Input                   |

| NMI                                                              | Nonmaskable interrupt request | Input                   |

| INTR                                                             | Interrupt request             | Input                   |

| CLK                                                              | System clock                  | Input                   |

| V <sub>cc</sub>                                                  | + 5-V                         | Power supply input      |

| GND                                                              | Ground                        | Power supply ground     |

#### TABLE - 1.5 : COMMON SIGNALS

#### TABLE - 1.6 : MINIMUM MODE SIGNALS [MN/MX=V<sub>cc</sub> (logic high)]

| Name | <b>Description</b> / Function | Туре             |  |

|------|-------------------------------|------------------|--|

| HOLD | Hold request                  | Input            |  |

| HLDA | Hold acknowledge              | Output           |  |

| WR   | Write control                 | Output, Tristate |  |

| M/IO | Memory / IO control           | Output, Tristate |  |

| DT/R | Data transmit/Receive         | Output, Tristate |  |

| DEN  | Data enable                   | Output, Tristate |  |

| ALE  | Address latch enable          | Output           |  |

| INTA | Interrupt acknowledge         | Output           |  |

#### TABLE - 1.7 : MAXIMUM MODE SIGNALS [MN/MX = Ground(Logic low)]

| Name         Description/Function                              |                                  | Туре             |

|----------------------------------------------------------------|----------------------------------|------------------|

| $\overline{RQ}/\overline{GT}_1, \overline{RQ}/\overline{GT}_0$ | Request/Grant bus access control | Bidirectional    |

| LOCK                                                           | Bus priority lock control        | Output, Tristate |

| $\overline{S}_{2}, \overline{S}_{1}, \overline{S}_{0}$         | Bus cycle status                 | Output, Tristate |

| QS <sub>1</sub> , QS <sub>0</sub>                              | Instruction queue status         | Output           |

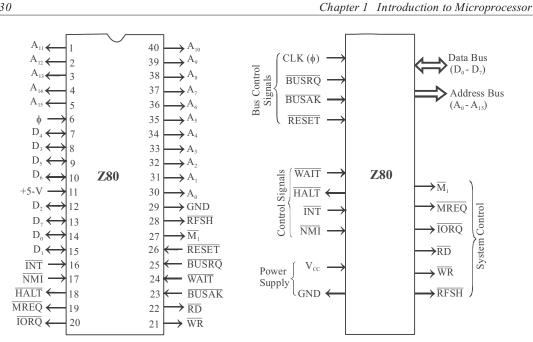

| interoprocessor (0000) inter its inpprocutions | Microprocessor | (8085) | ) And Its | Ap | plications |

|------------------------------------------------|----------------|--------|-----------|----|------------|

|------------------------------------------------|----------------|--------|-----------|----|------------|

#### **Common signals**

The signals common for minimum and maximum mode are listed in Table-1.5. The lower sixteen lines of address are multiplexed with data and the upper four lines of address are multiplexed with status signals. During the first clock period of a bus cycle, the entire 20-bit address is available on these lines. During all other clock period of a bus cycle, the data and status signals will be available on these lines.

The status signals on  $S_3$  and  $S_4$  specifies the segment register used for calculating physical address. The output on the status lines  $S_3$  and  $S_4$  when the processor is accessing various segments are listed in Table-1.8.

| Status                | signal         |                    |

|-----------------------|----------------|--------------------|

| <b>S</b> <sub>4</sub> | S <sub>3</sub> | Segment register   |

| 0                     | 0              | Extra segment      |

| 0                     | 1              | Stack segment      |

| 1                     | 0              | Code or no segment |

| 1                     | 1              | Data segment       |

#### **TABLE - 1.8 : STATUS SIGNAL DURING MEMORY SEGMENT ACCESS**

The status lines  $S_3$  and  $S_4$  can be used to expand the memory upto 4 Mb. The status line  $S_5$  indicates the status of 8086 interrupt enable flag. A **low** on the line  $S_6$  indicates that 8086 is on the bus (i.e., it indicates that 8086 is the bus master) and during hold acknowledge this pin is driven to **high impedance** state. The output signal  $\overline{BHE}$  on the first T-state of a bus cycle is maintained as status signal  $S_7$  on the same pin.

The 8086 outputs a **low** on BHE pin during read, write and interrupt acknowledge cycles when the data is to be transferred to the high order data bus. The  $\overline{BHE}$  can be used in conjunction with AD<sub>0</sub> to select memory banks.

When the processor reads from memory or an IO location, it asserts  $\overline{\text{RD}}$  low. The TEST input is tested by the WAIT instruction. The 8086 will enter a wait state after execution of the WAIT instruction, and it will resume execution only when TEST is made low by an external hardware. This is used to synchronize an external activity to the processor internal operation. TEST input is synchronized internally during each clock cycle on the leading edge of the clock signal.

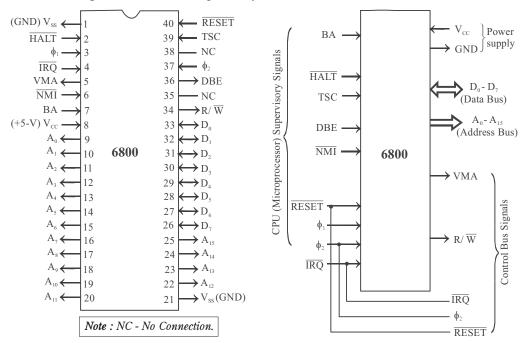

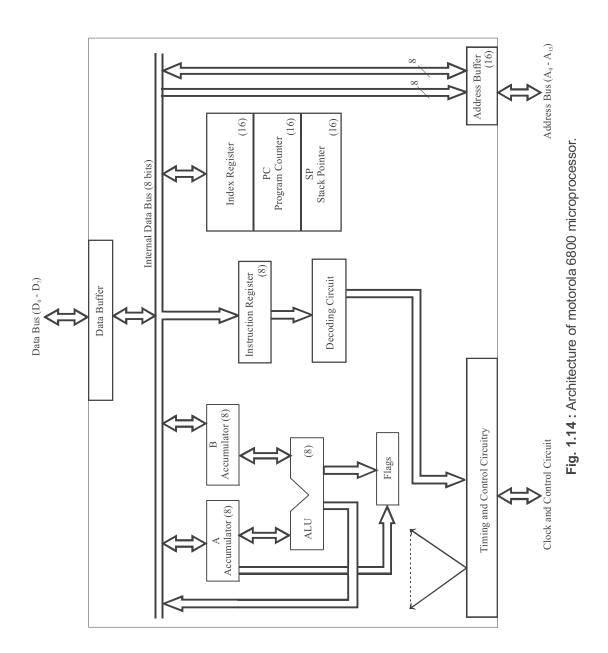

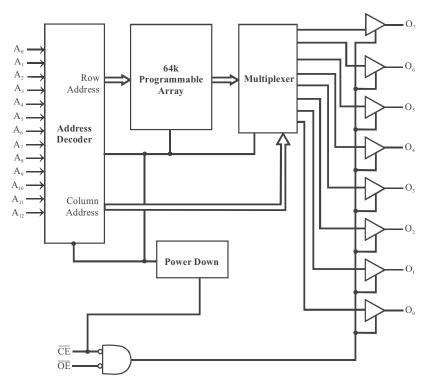

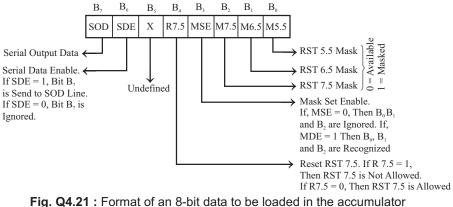

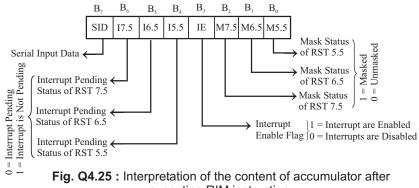

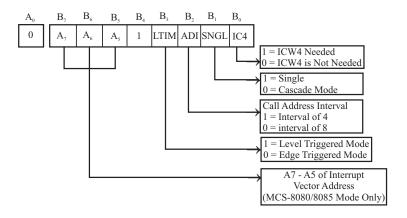

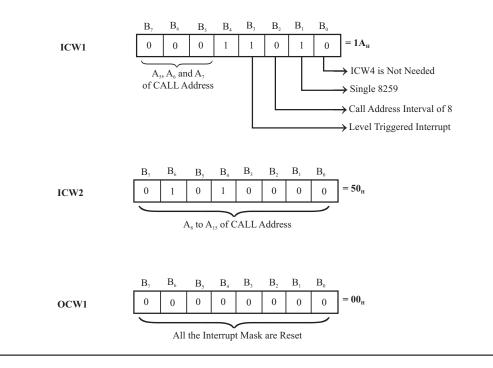

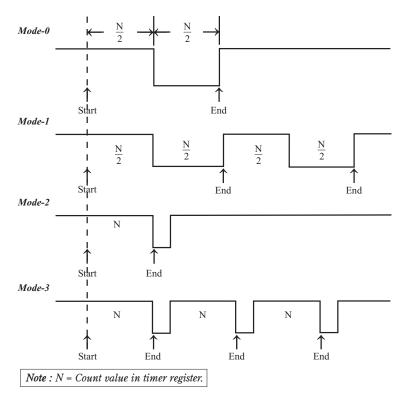

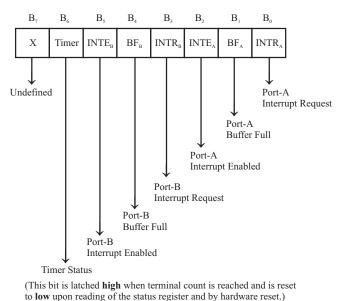

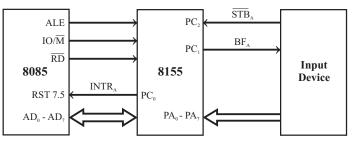

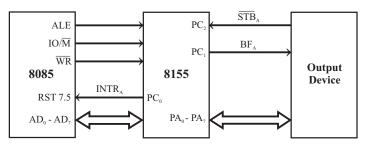

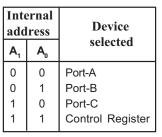

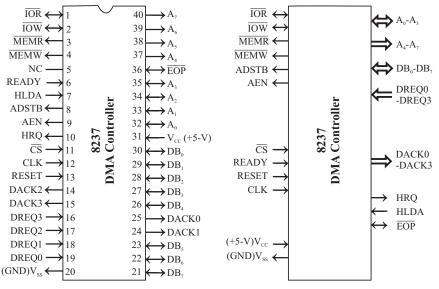

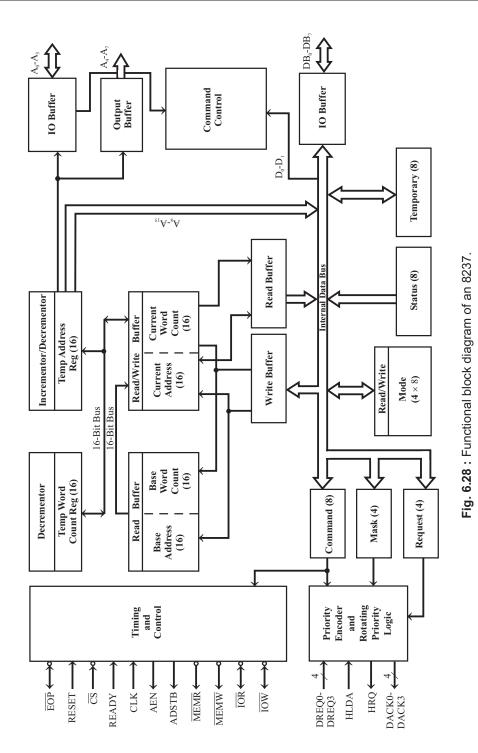

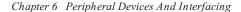

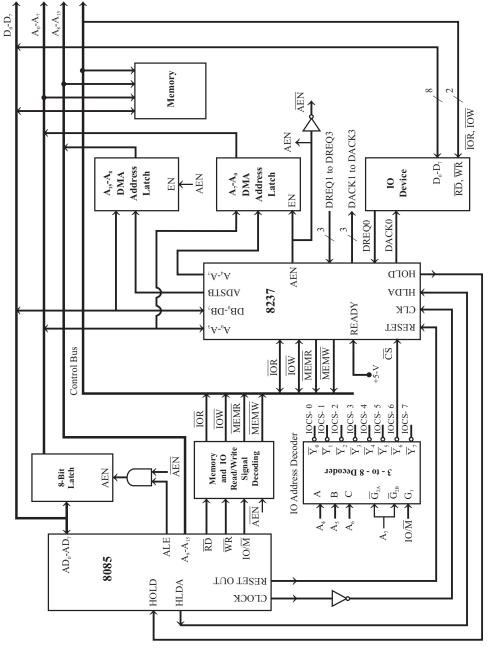

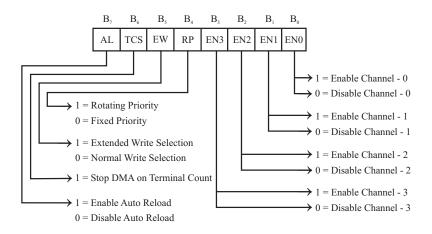

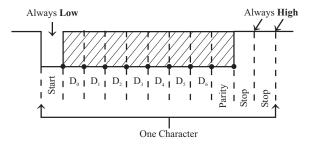

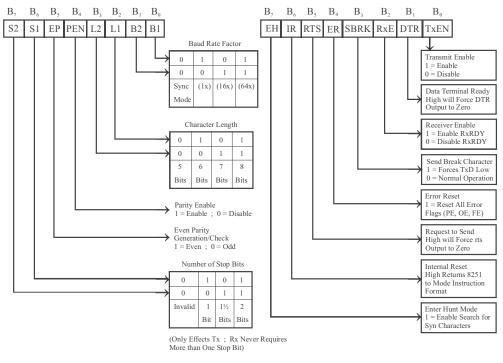

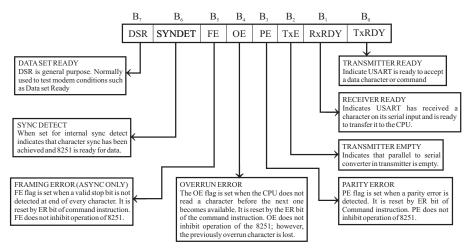

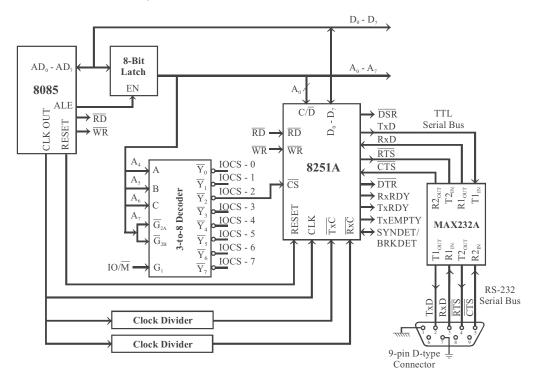

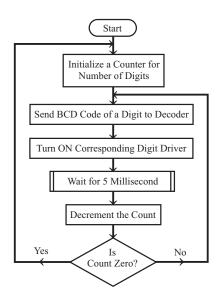

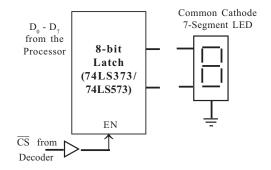

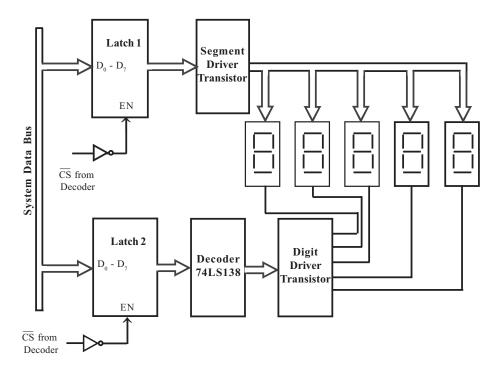

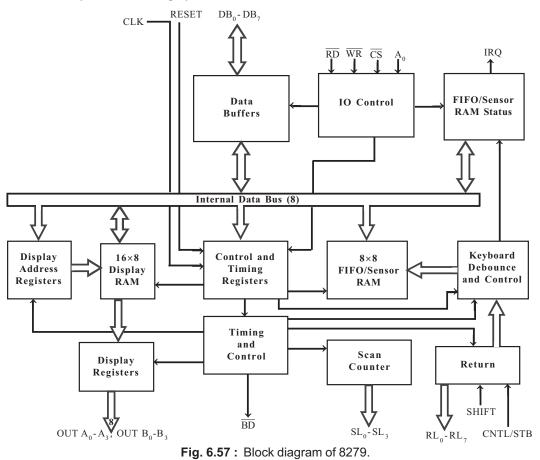

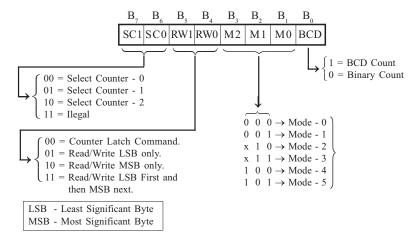

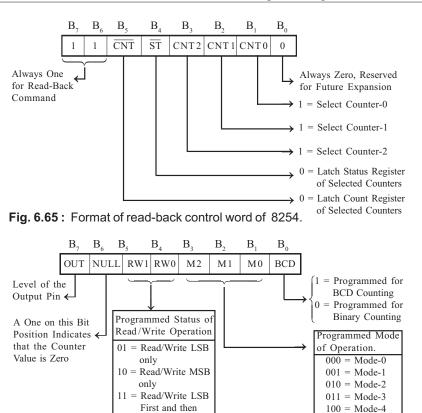

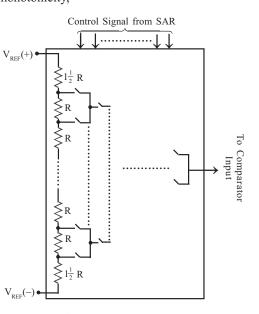

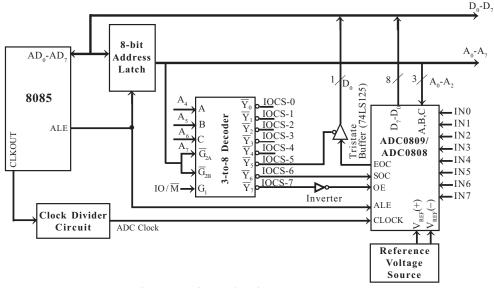

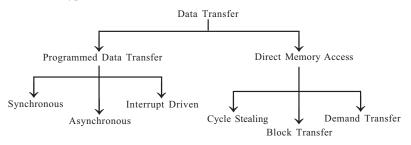

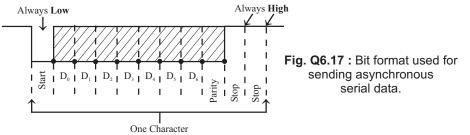

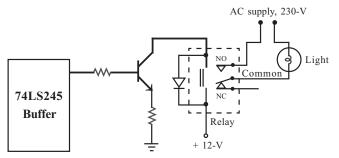

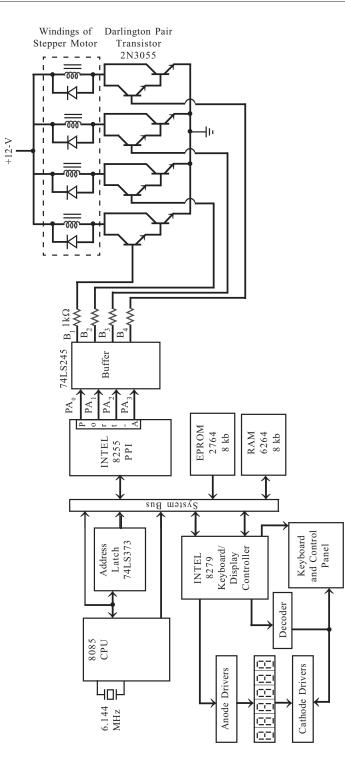

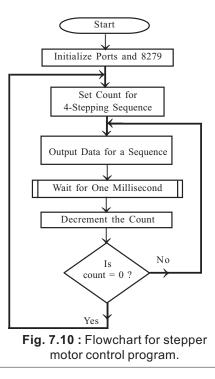

INTR is the maskable interrupt and INTR must be held **high** until it is recognized to generate an interrupt signal. NMI is the nonmaskable interrupt input activated by a leading edge signal.