# Basic Electrical and Electronics Engineering-II

WBUT-2016

Fifth Edition

# About the Authors

Abhijit Chakrabarti, PhD (Technology), is former Vice Chairman and Chairman (acting) of West Bengal State Council of Higher Education, West Bengal. He is also the Professor and former HOD of the Department of Electrical Engineering, Indian Institute of Engineering, Science and Technology Shibpur, Howrah, West Bengal. He has also served as the former Vice Chancellor of Jadavpur University, Kolkata. He has nearly eight years of industrial experience and around twenty-five years of teaching and research experience. He is a fellow of the Institution of Engineers (India) and has published/presented 129 research papers in international and national journals and conferences including IEEE Transaction, Elsevier, etc. He has published numerous books on Electrical Engineering. Professor Chakrabarti is the recipient of Pandit Madan Mohan Malviya award and the Power Medal, Merit and Best Paper awards (twice) from Central Electricity Authority, India, and an International Conference, China. His areas of interest include power systems, electric circuits, and power electronics and drives.

**Sudipta Debnath,** PhD in (Engineering), is the Associate Professor, Department of Electrical Engineering, Jadavpur University, Kolkata. She has received the Career Award from AICTE, Govt. of India, and Young Scientist recognition from DST, Govt. of India. She is also the recipient of a certificate of merit from Institution of Engineers, India. She has published/presented 35 research papers in international and national journals and conferences. She has nearly one year of industrial experience and 18 years of teaching and research experience. Her areas of interest include power systems, electrical machines and soft computing techniques.

Soumitra Kumar Mandal is Professor at National Institute of Technical Teachers' Training and Research, Kolkata. He obtained a BE (Electrical Engineering) from Bengal Engineering College, Shibpur, Calcutta University, and an MTech (Electrical Engineering) with specialisation in Power Electronics from Institute of Technology, Banaras Hindu University, Varanasi. Thereafter, he obtained a PhD degree from Punjab University, Chandigarh. He started his career as a lecturer of Electrical Engineering, SSGM College of Engineering, Shegaon. After that he joined as a lecturer at Punjab Engineering College, Chandigarh, and served there from March 1999 to January 2004. From February 2004, he joined National Institute of Technical Teachers' Training and Research, Kolkata, and is presently the Professor in Electrical Engineering. He is also a life member of ISTE and a member of IE. Throughout his academic career, he has published about twenty research papers in national and international journals and presented many papers in national and international conferences. His research interests are in the field of computer controlled drives, microprocessor and microcontroller-based system design, embedded system design and neuro-fuzzy computing.

# Basic Electrical and Electronics Engineering-II

# WBUT-2016

# Fifth Edition

# Part I: Electrical Engineering-II

Authored by

# Abhijit Chakrabarti

Professor and Former HOD, Department of Electrical Engineering Indian Institute of Engineering Science and Technology Shibpur, Howrah, West Bengal and Former Vice Chancellor, Jadavpur University, Kolkata Former Vice Chairman and Chairman (acting) West Bengal State Council of Higher Education, Kolkata

Sudipta Debnath

Associate Professor Department of Electrical Engineering Jadavpur University, Kolkata

# Part II: Electronics Engineering-II

Authored by Soumitra Kumar Mandal

Professor National Institute of Technical Teachers' Training and Research Kolkata

# McGraw Hill Education (India) Private Limited

NEW DELHI

McGraw Hill Education Offices

New Delhi New York St Louis San Francisco Auckland Bogotá Caracas Kuala Lumpur Lisbon London Madrid Mexico City Milan Montreal San Juan Santiago Singapore Sydney Tokyo Toronto

#### Ication McGraw Hill Education (India) Private Limited

Published by McGraw Hill Education (India) Private Limited, P-24, Green Park Extension, New Delhi 110 016.

#### Basic Electrical and Electronics Engineering-II, 5e (WBUT-2016)

Copyright © 2016, 2015, 2013, by McGraw Hill Education (India) Private Limited

No part of this publication may be reproduced or distributed in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise or stored in a database or retrieval system without the prior written permission of the publishers. The program listings (if any) may be entered, stored and executed in a computer system, but they may not be reproduced for publication.

This edition can be exported from India only by the publishers, McGraw Hill Education (India) Private Limited.

Print Edition: ISBN-13: 978-93-85880-91-9 ISBN-10: 93-85880-91-8

Managing Director: *Kaushik Bellani* Director—Product (Higher Education and Professional): *Vibha Mahajan*

Manager—Product Development: *Koyel Ghosh* Specialist—Product Development: *Piyali Chatterjee* Head—Production (Higher Education and Professional): *Satinder S Baveja* Senior Production Executive: *Jagriti Kundu* Senior Graphic Designer—Cover: *Meenu Raghav* AGM—Product Management (Higher Education and Professional): *Shalini Jha* Manager—Product Management: *Ritwick Dutta*

General Manager—Production: *Rajender P Ghansela* Manager—Production: *Reji Kumar*

Information contained in this work has been obtained by McGraw Hill Education (India), from sources believed to be reliable. However, neither McGraw Hill Education (India) nor its authors guarantee the accuracy or completeness of any information published herein, and neither McGraw Hill Education (India) nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw Hill Education (India) and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

Typeset at Tej Composers, WZ-391, Madipur, New Delhi 110063 and printed at

Cover:

Visit us at: www.mheducation.co.in

# CONTENTS

| Preface<br>Roadma | xiii xiii xvii                                                                     |

|-------------------|------------------------------------------------------------------------------------|

|                   | Part I—Basic Electrical Engineering-II                                             |

| 1. Ele            | ctrostatics I.1.1-I.1.68                                                           |

| 1.1               | Introduction <i>I.1.1</i>                                                          |

|                   | Coulomb's Law 1.1.1                                                                |

| 1.3               | Permittivity 1.1.2                                                                 |

|                   | Electric Flux and Flux Density 1.1.3                                               |

|                   | Electric Potential and Potential Difference 1.1.3                                  |

|                   | Expression for Potential at a Point within an Electric Field 1.1.4                 |

|                   | Electric Field Intensity 1.1.5                                                     |

|                   | Electric Field Intensity and Potential of Isolated Point Charge $(Q)$ 1.1.5        |

|                   | Potential Due to a Group of Charges 1.1.6                                          |

|                   | Electric Field Intensity and Potential Gradient 1.1.6                              |

|                   | Relation between Electric Flux Density and Electric Field Intensity <i>1.1.7</i>   |

|                   | Electric Potential Energy <i>1.1.7</i>                                             |

|                   | Relation between Electric Field Strength and Potential <i>1.1.8</i>                |

|                   | Electric Field Inside a Conductor 1.1.9                                            |

|                   | Continuous Charge Distribution 1.1.10                                              |

|                   | Gauss's Law and its Derivation 1.1.11                                              |

|                   | Application of Gauss's Law <i>1.1.12</i>                                           |

|                   | Capacitor and Capacitance 1.1.18                                                   |

|                   | Types of Capacitors Commonly Used 1.1.20                                           |

|                   | Capacitance of a Parallel-plate Capacitor 1.1.21                                   |

|                   | Capacitance of a Multi-plate Capacitor 1.1.22                                      |

|                   | Capacitance of a Parallel-plate Capacitor with Composite Dielectrics <i>1.1.22</i> |

|                   | Capacitance of an Isolated Sphere 1.1.24                                           |

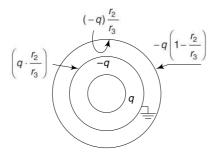

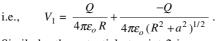

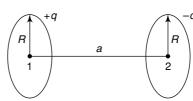

|                   | Capacitance of Concentric Spheres 1.1.24                                           |

| 1.25              | Capacitance of a Parallel Plate Capacitor when an Uncharged                        |

| 1.00              | Metal Slab is Introduced between Plates 1.1.26                                     |

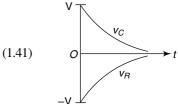

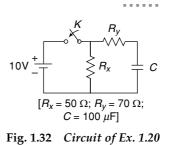

|                   | Expression of Instantaneous Current and Voltage in a Capacitor 1.1.32              |

|                   | Charging and Discharging of Capacitance 1.1.33                                     |

|                   | Energy Stored in a Capacitor 1.1.38                                                |

| 1.29              | Capacitance of Two Co-axial Cylinders 1.1.40                                       |

|                   | Additional Examples 1.1.41                                                         |

|                   | Exercises 1.1.60                                                                   |

|                   | University Questions with Answers I.1.66                                           |

# 8

#### Contents

#### 2. DC Machines

#### I.2.1 – I.2.52

I.3.1-I.3.68

- 2.1 Introduction 1.2.1

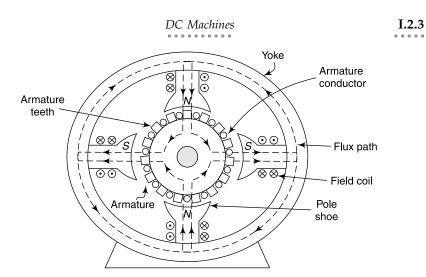

- 2.2 Principal Parts of a DC Machine *1.2.1*

- 2.3 Magnetic Flux Path in a DC Generator 1.2.2

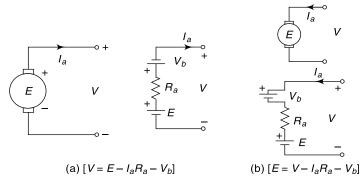

- 2.4 Equivalent Circuit of a DC Machine 1.2.2

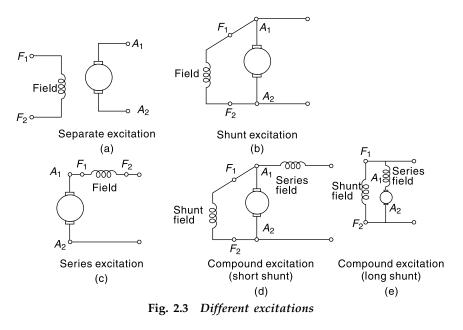

- 2.5 Different Types of Excitations in DC Machine 1.2.3

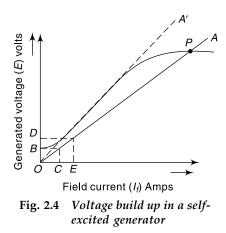

- 2.6 Process of Voltage Build up in Self-excited Generator 1.2.5

- 2.7 EMF Equation of a DC Machine 1.2.6

- 2.8 Types of Windings 1.2.6

- 2.9 Armature Reaction 1.2.8

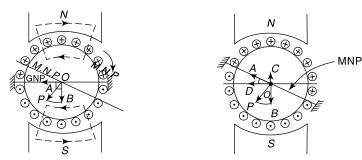

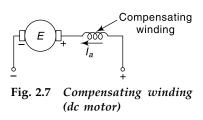

- 2.10 Commutation 1.2.9

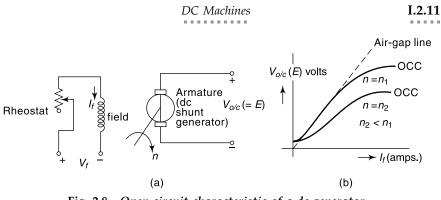

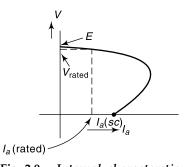

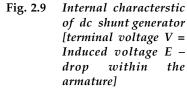

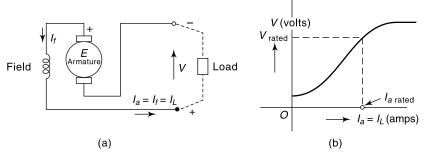

- 2.11 Characteristics of DC Generators 1.2.10

- 2.12 Principle of Operation of a DC Motor *1.2.14*

- 2.13 Back EMF 1.2.14

- 2.14 Torque Equation of a DC Motor 1.2.14

- 2.15 Speed Equation of a DC Motor 1.2.19

- 2.16 Speed Regulation of DC Motor *1.2.20*

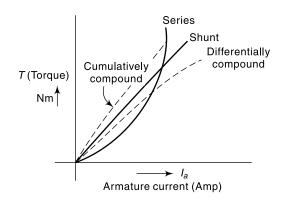

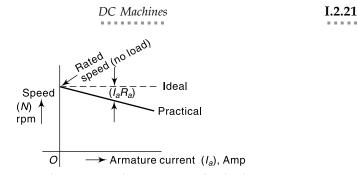

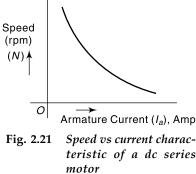

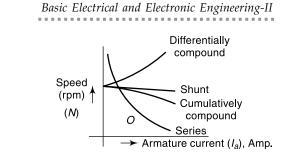

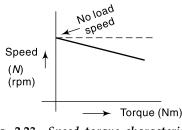

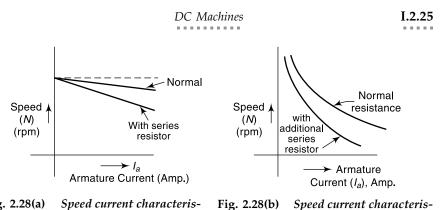

- 2.17 Speed vs. Armature Current Characteristic of DC Motor  $(N/I_a \text{ Characteristics})$  1.2.20

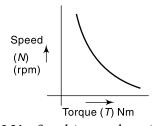

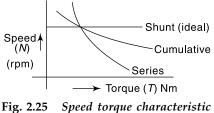

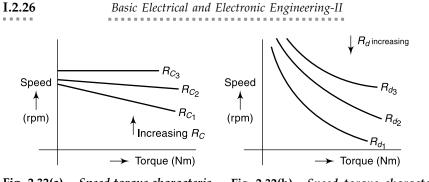

- 2.18 Speed Torque Characteristic of DC Motors *1.2.22*

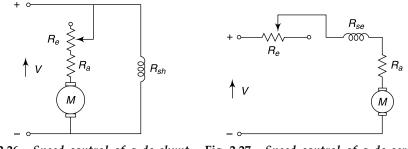

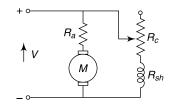

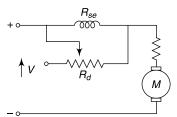

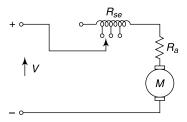

- 2.19 Speed Control of DC Motors 1.2.24

- 2.20 Losses in a DC Machine *1.2.28*

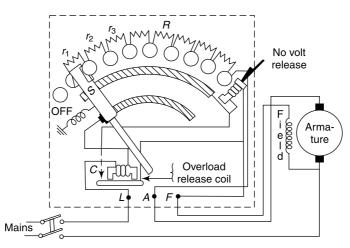

- 2.21 DC Motor Starting 1.2.33

- 2.22 Reversal of Rotation of DC Motor 1.2.35

- 2.23 DC Machine Applications 1.2.35 Additional Examples 1.2.36 Exercises 1.2.43 Multiple Choice Questions 1.2.46 University Questions with Answers 1.2.47

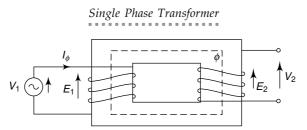

#### 3. Single Phase Transformer

- 3.1 Definition 1.3.1

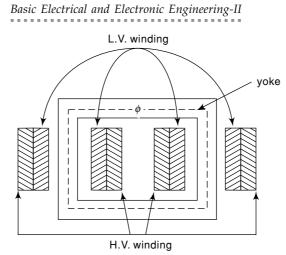

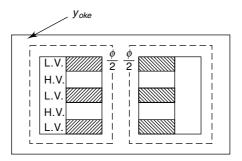

- 3.2 Construction of Single-phase Transformers 1.3.1

- 3.3 Principle of Operation *1.3.2*

- 3.4 EMF Equation 1.3.3

- 3.5 Transformation Ratio (or Turns Ratio) 1.3.3

- 3.6 Impedance Transformation 1.3.4

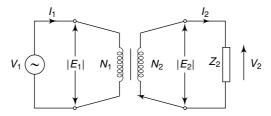

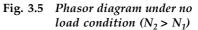

- 3.7 No Load Operation of a Transformer 1.3.8

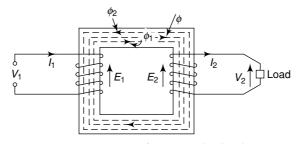

- 3.8 Working of a Transformer on Load 1.3.9

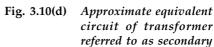

- 3.9 Equivalent Circuit of Transformer 1.3.12

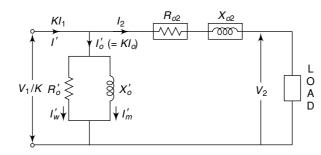

- 3.10 Approximate Equivalent Circuit 1.3.14

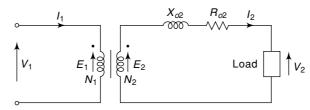

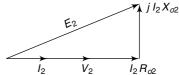

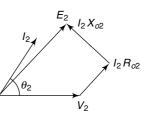

- 3.11 Regulation of a Transformer 1.3.15

- 3.12 Condition for Zero (Minimum) Regulation 1.3.17

- 3.13 Losses and Efficiency of Transformer 1.3.23

- 3.14 Condition for Maximum Efficiency 1.3.24

vi

#### Contents

- 3.15 Expression for Load at which Efficiency is Maximum 1.3.24

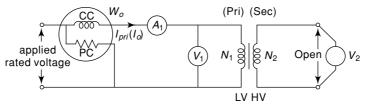

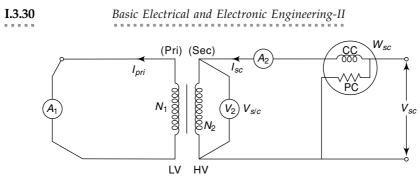

- 3.16 Testing of Transformers 1.3.28

- 3.17 Single-phase Auto Transformer 1.3.33

- 3.18 Transformer Cooling 1.3.34

- 3.19 Conservator and Breather 1.3.35

- 3.20 Distribution Transformers and Power Transformers 1.3.35

- 3.21 Name Plate and Ratings 1.3.36

- 3.22 All Day Efficiency 1.3.36 Additional Examples 1.3.36 Exercises I.3.52 Multiple Choice Questions 1.3.56 University Questions with Answers 1.3.58

#### 4. Three-Phase System

#### 4.1 Three-Phase Electric System 1.4.1

- 4.2 Advantages of a Three-Phase System 1.4.1

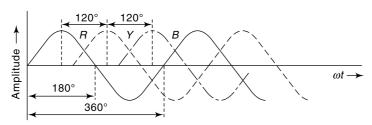

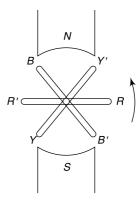

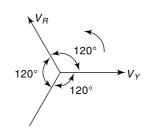

- 4.3 Generation of Three-Phase Balanced Voltage 1.4.1

- 4.4 Interconnection of Phases *1.4.2*

- 4.5 One-line Equivalent Circuit for 1.4.7 Balanced Loads 1.4.7

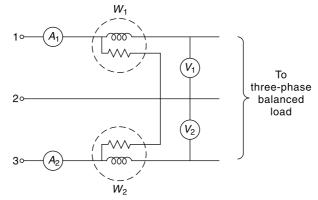

- 4.6 Measurement of Power in a Three-Phase Three-Wire System 1.4.12

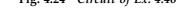

- 4.7 Measurement of Power for a Three-Phase System Using Two Wattmeters (Assuming Balanced Load and Sinusoidal Voltages and Currents) *I.4.14*

- 4.8 Unbalanced Four-Wire Star Connected Load 1.4.15

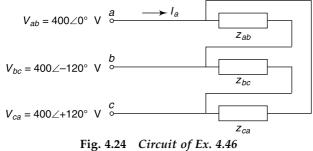

- 4.9 Unbalanced Delta Connected Load 1.4.15

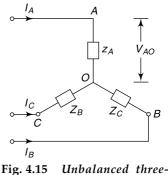

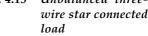

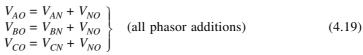

- 4.10 Unbalanced Three-Wire Star Connected Load 1.4.15 Additional Examples 1.4.20 Exercises I.4.36 Multiple Choice Questions 1.4.38 University Questions with Answers 1.4.40

#### 5. Three-Phase Induction Motors

- 5.1 Introduction 1.5.1

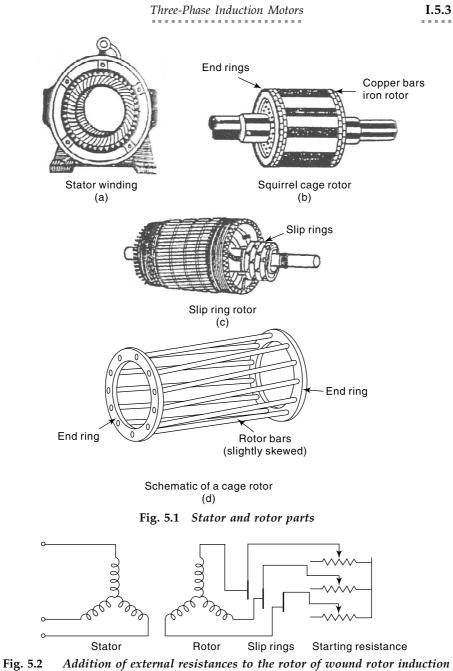

- 5.2 Construction of Induction Machines 1.5.2

- 5.3 Comparison of Squirrel Cage and Wound Rotors 1.5.4

- 5.4 Advantages and Disadvantages of a Three-phase Induction Motor 1.5.4

- 5.5 Principle of Operation 1.5.4

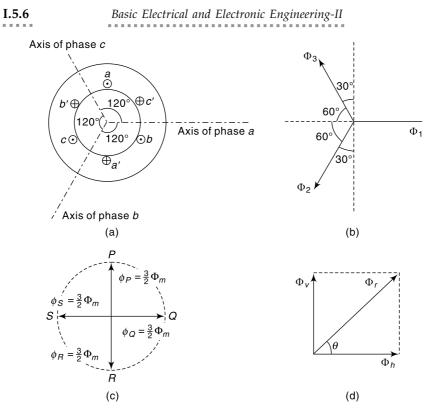

- 5.6 Concept of Production of Rotating Field 1.5.5

- 5.7 The Concept of Slip 1.5.7

- 5.8 Frequency of Rotor Voltages and Currents 1.5.8

- 5.9 Torque Expression of an Induction Motor 1.5.11

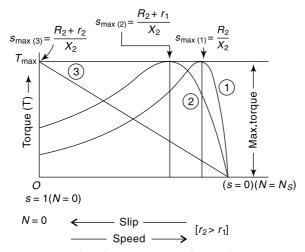

- 5.10 Torque Slip Characteristics of a Three-phase Induction Motor 1.5.19

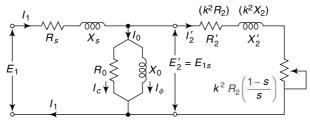

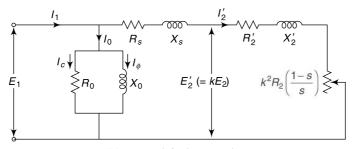

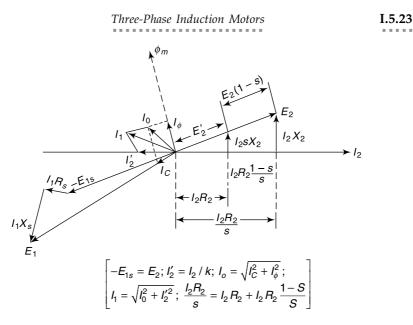

- 5.11 Equivalent Circuit of Induction Motor 1.5.21

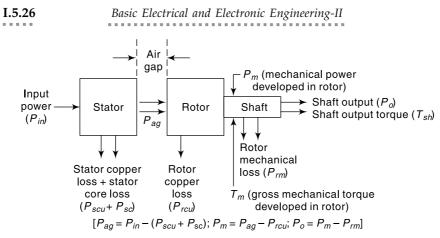

- 5.12 Losses and Efficiency 1.5.22

#### I.4.1-I.4.43

vii

I.5.1 - I.5.62

| C  | 20 | )K | ıt | e  | n  | ts | ; |

|----|----|----|----|----|----|----|---|

| 10 |    | н. |    | н. | н. | н. |   |

- 5.13 Determination of Motor Efficiency *1.5.27*

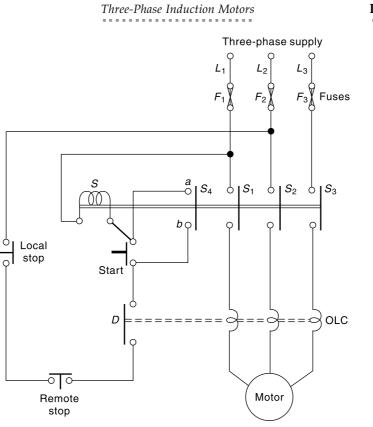

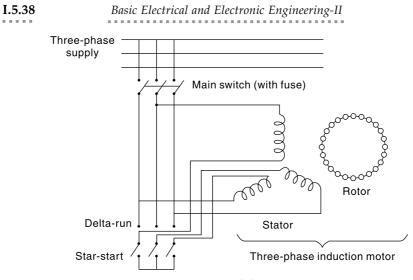

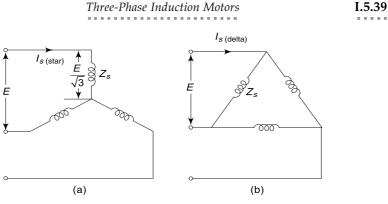

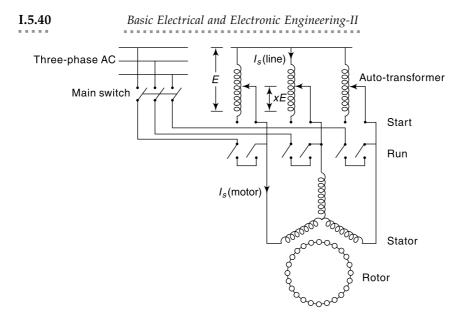

- 5.14 Starting of Three-phase Induction Motors 1.5.36

- 5.15 Comparison among Direct On Line Starter, Star Delta Starter and Auto-transformer Starter *1.5.40*

- 5.16 Speed Control of a Three-phase Induction Motor 1.5.41

- 5.17 Reversal of Rotation 1.5.42 Additional Examples 1.5.44 Exercises 1.5.51 Multiple Choice Questions 1.5.58 University Questions with Answers 1.5.60

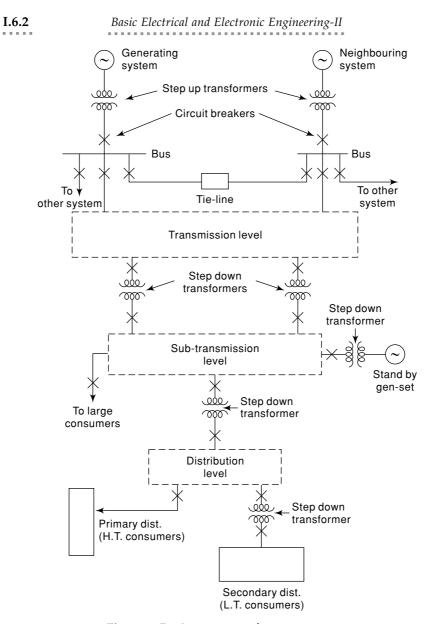

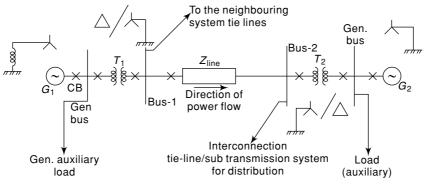

#### 6. Structure of a Power System

I.6.1 – I.6.5

- 6.1 Structure of a Power System 1.6.1

- 6.2 Power Distribution Systems *1.6.3*

- 6.3 Power System Representation 1.6.4 Exercises 1.6.4 University Questions with Answers 1.6.5

#### Part II: Basic Electronics Engineering-II

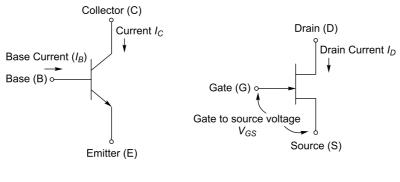

#### 1. Field Effect Transistors

II.1.1 – II.1.84

- 1.1 Introduction *II.1.1*

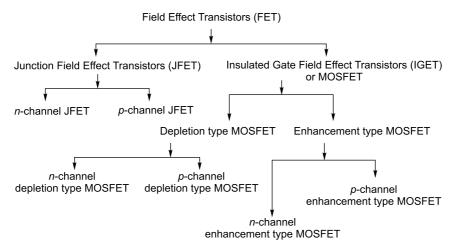

- 1.2 Classification of Field Effect Transistor *II.1.2*

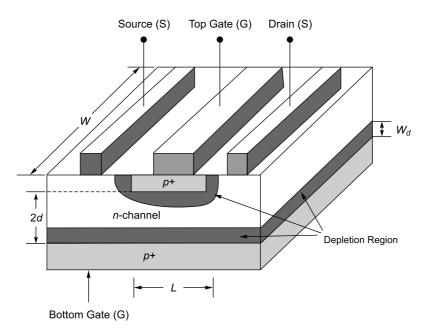

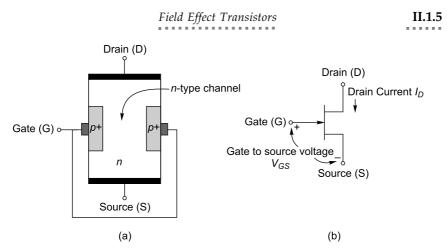

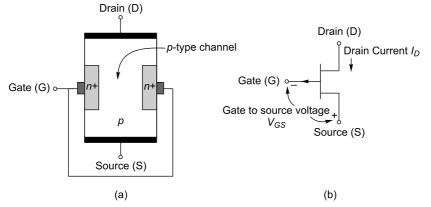

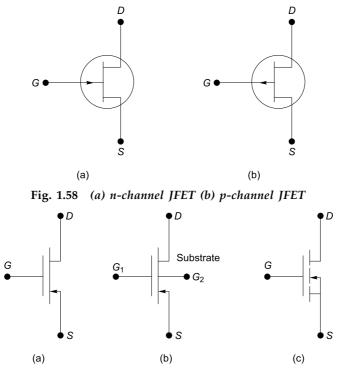

- 1.3 Junction Field Effect Transistor II.1.3

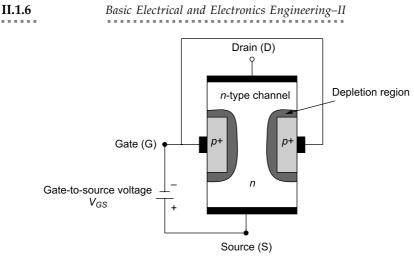

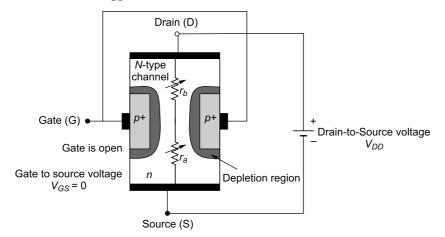

- 1.4 Operation of JEET *II.1.7*

- 1.5 Characteristics of JEET II.1.12

- 1.6 Characteristic Parameter of JEET II.1.18

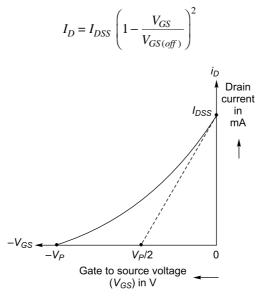

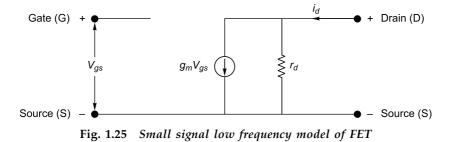

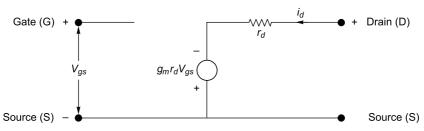

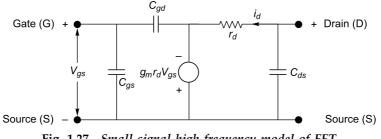

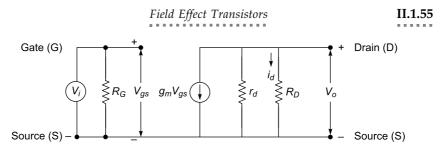

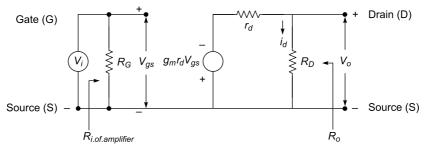

- 1.7 Small Signal Model of FET *II.1.20*

- 1.8 Comparison Between FET and BJT *II.1.22*

- 1.9 Comparison Between N-Channel FET and P-Channel FET II.1.22

- 1.10 Applications of JEET *II.1.23*

- 1.11 Metal Oxide Semiconductor (MOS) Field Effect Transistor or MOSFET *II.1.25*

- 1.12 MOS Capacitor II.1.25

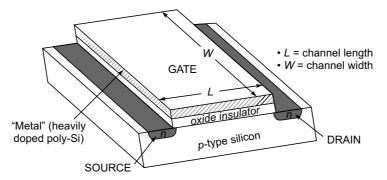

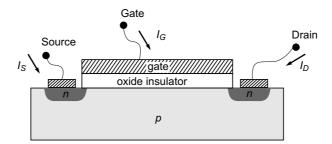

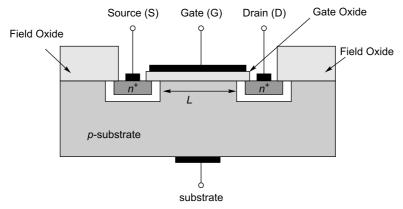

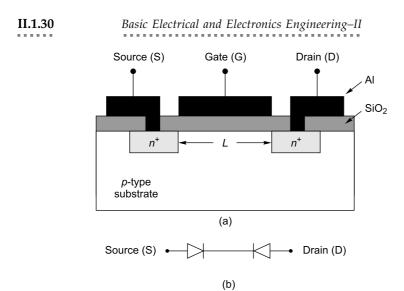

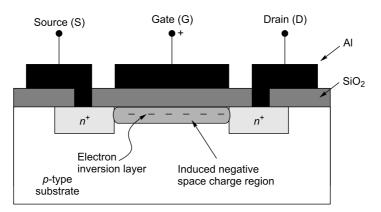

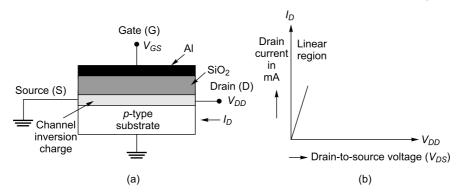

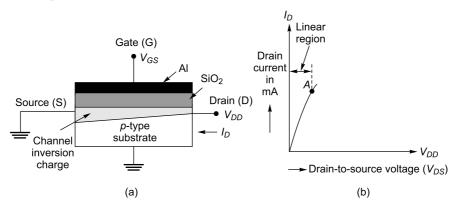

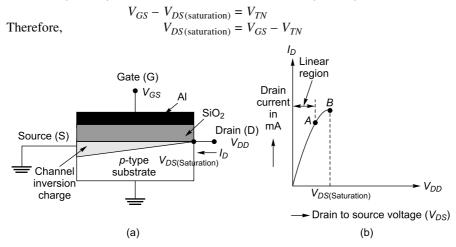

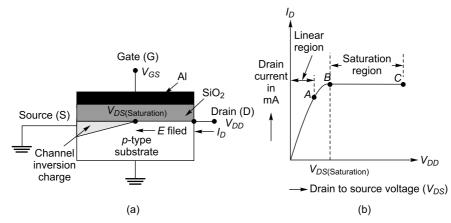

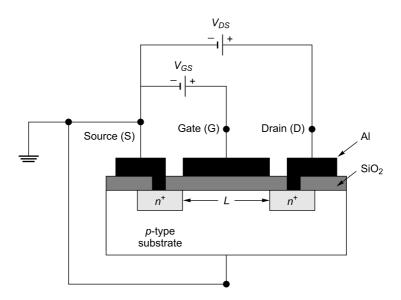

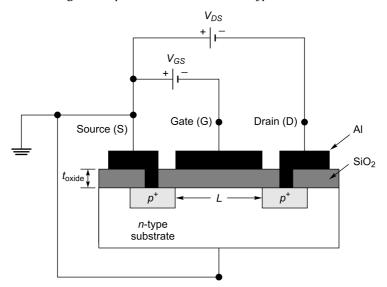

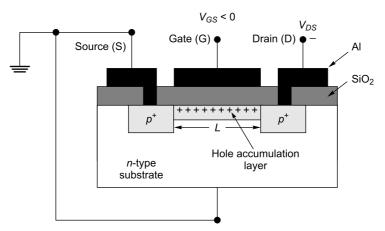

- 1.13 n-Channel Enhancement MOSFET II.1.28

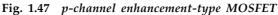

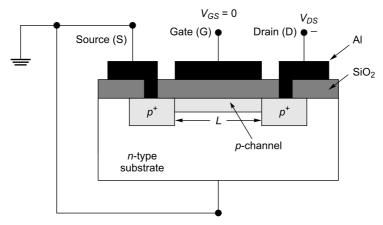

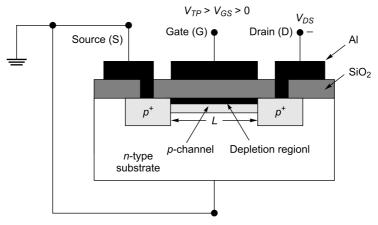

- 1.14 *p*-Channel Enhancement MOSFET *II.1.35*

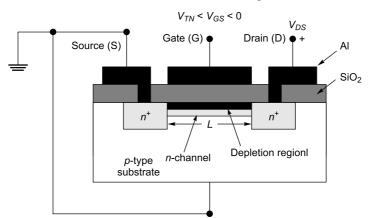

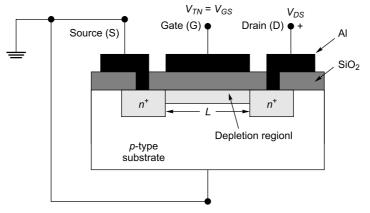

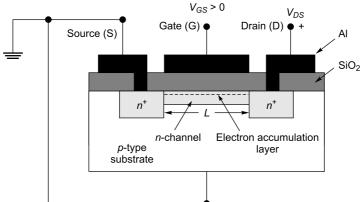

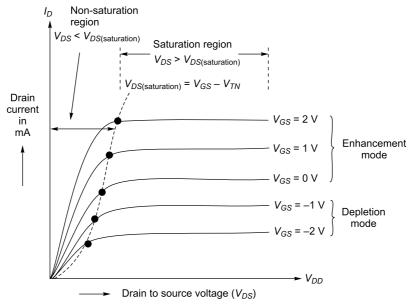

- 1.15 *n*-Channel Depletion type MOSFET *II.1.37*

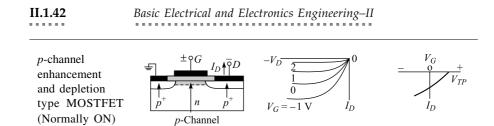

- 1.16 *p*-Channel Depletion type MOSFET *II.1.40*

- 1.17 Current Voltage Relationship between *n*-Channel MOSFET and *p*-Channel MOSFET *II.1.42*

- 1.18 Comparison Between NMOS and PMOS II.1.42

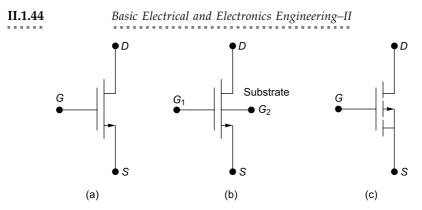

- 1.19 Circuit Symbols of JEET and MOSFET *II.1.43*

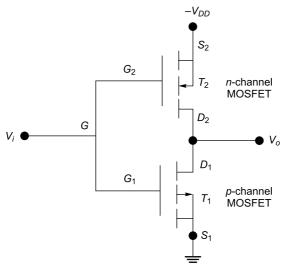

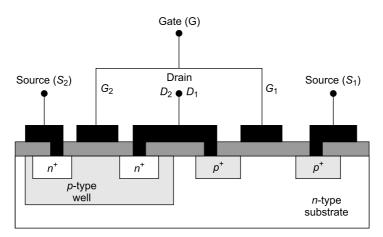

- 1.20 Complementary MOSFET (CMOS) II.1.44

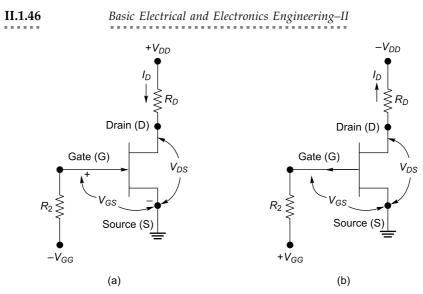

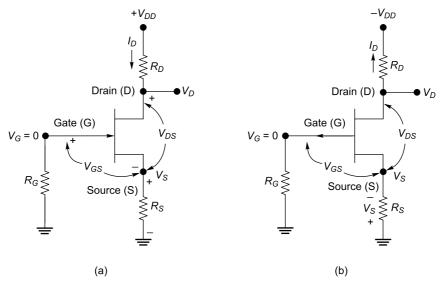

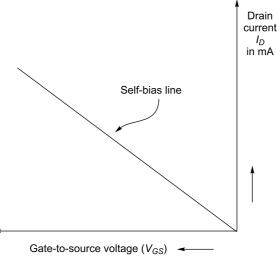

- 1.21 Biasing the FET *II.1.45*

viii

Contents

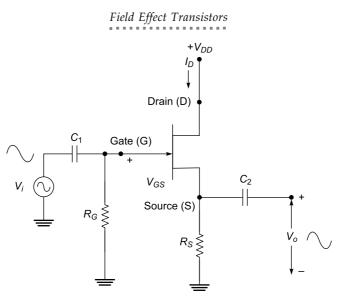

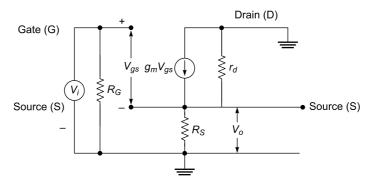

1.22 FET Amplifier Configurations *II.1.53 Exercises II.1.66 Multiple Choice Questions II.1.72 University Questions with Answers II.1.78*

#### 2. Feedback Amplifier

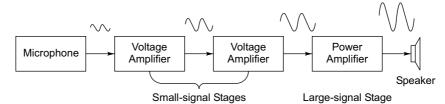

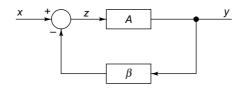

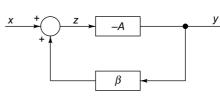

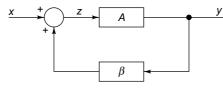

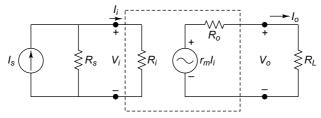

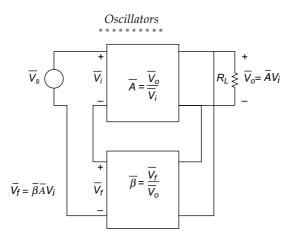

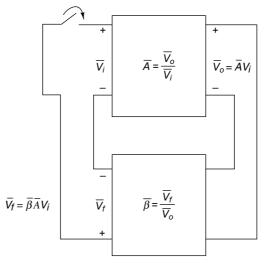

# 2.1 Introduction II.2.1

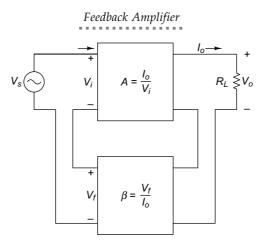

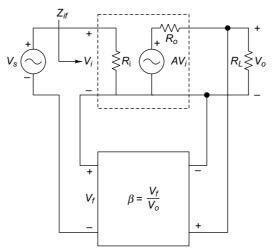

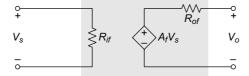

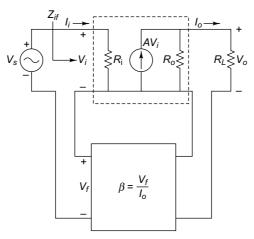

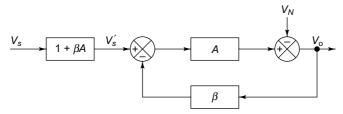

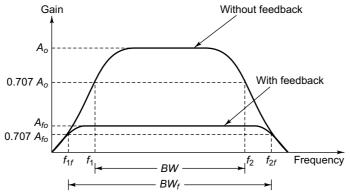

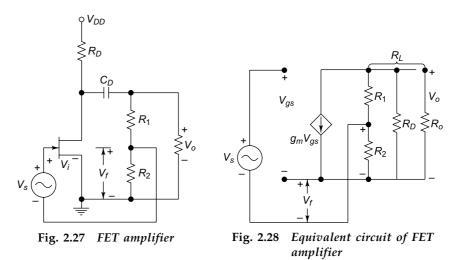

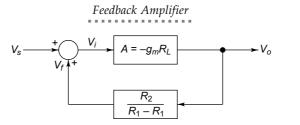

- 2.2 Feedback Amplifier *II.2.2*

- 2.3 Classification of Amplifiers *II.2.7*

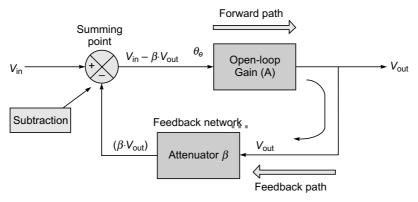

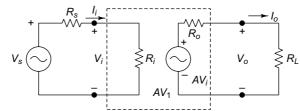

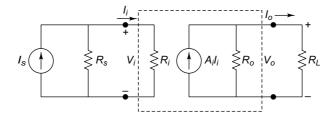

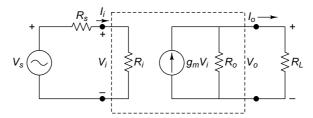

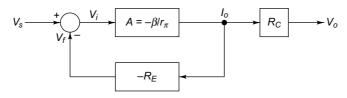

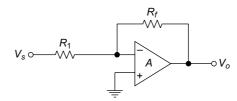

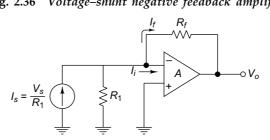

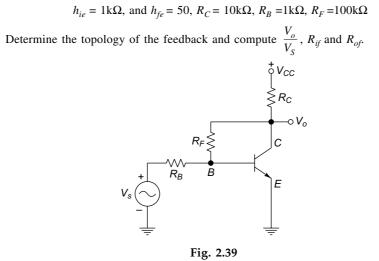

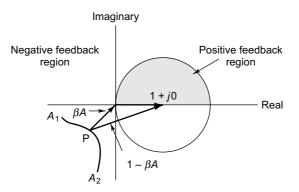

- 2.4 Generalised Concept of Feedback Amplifier II.2.11

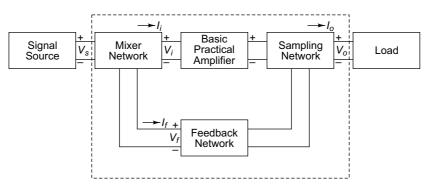

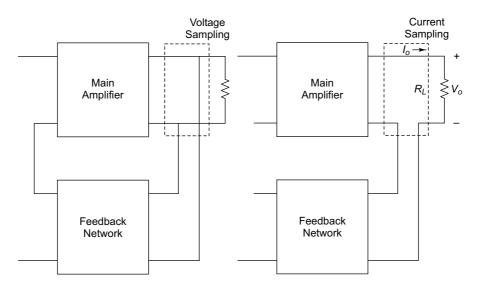

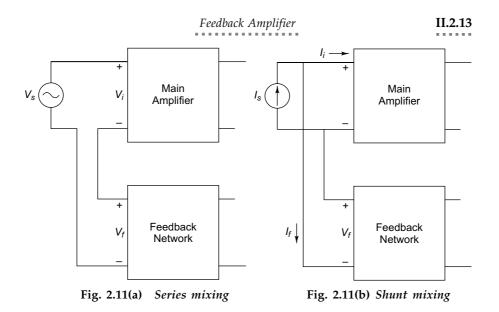

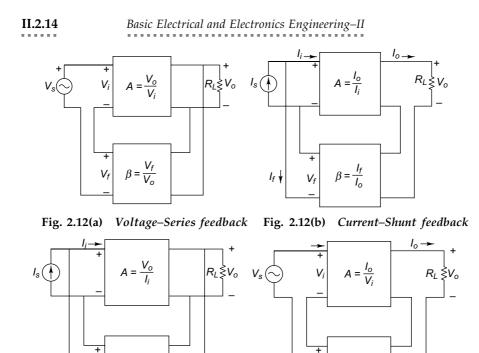

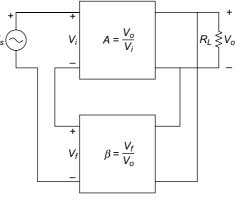

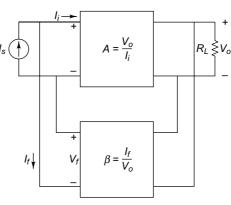

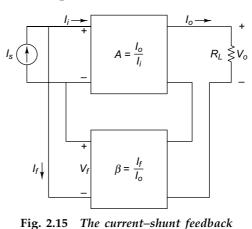

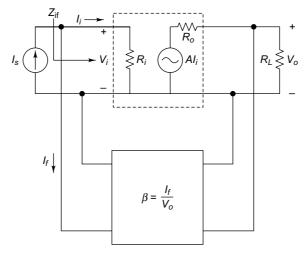

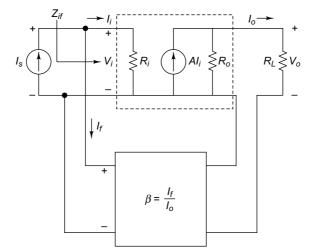

- 2.5 Topologies of a Feedback Amplifier *II.2.13*

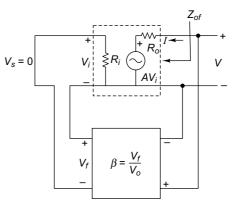

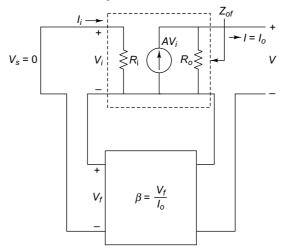

- 2.6 Effect of Feedback on Impedances *II.2.17*

- 2.7 Properties of Feedback Amplifiers *II.2.27*

- 2.8 Method of Analysis of a Feedback Amplifier *II.2.32*

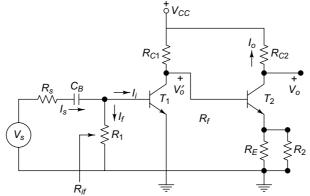

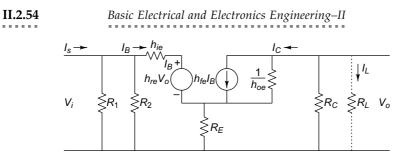

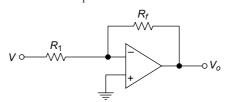

- 2.9 Practical Feedback Circuits II.2.33

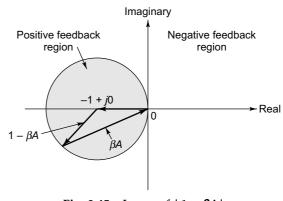

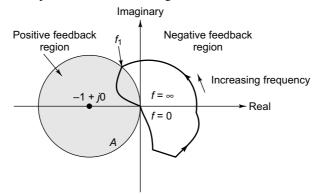

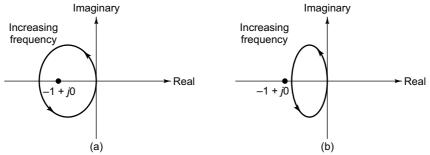

- 2.10 Stability of a Feedback Amplifier *II.2.44 Exercises II.2.45 Multiple Choice Questions II.2.48 University Questions with Answers II.2.51*

#### 3. Oscillators

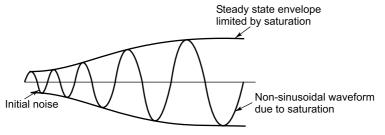

### 3.1 Introduction II.3.1

- 3.2 Classification of Oscillators II.3.1

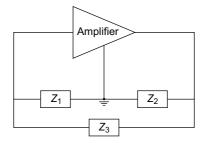

- 3.3 The Basic Oscillator II.3.3

- 3.4 Oscillator Operation II.3.4

- 3.5 Phase Shift in Oscillation *II.3.8*

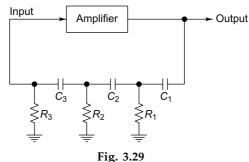

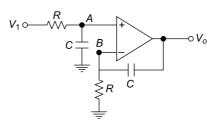

- 3.6 Phase Shift Oscillator *II.3.9*

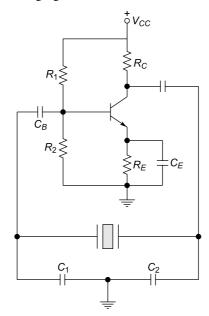

- 3.7 BJT Phase Shift Oscillator II.3.11

- 3.8 FET Phase Shift Oscillator II.3.14

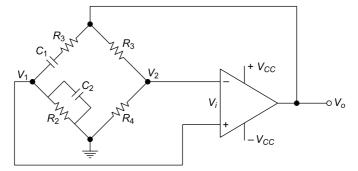

- 3.9 Wein Bridge Oscillator *II.3.16*

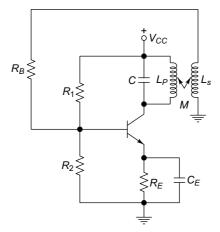

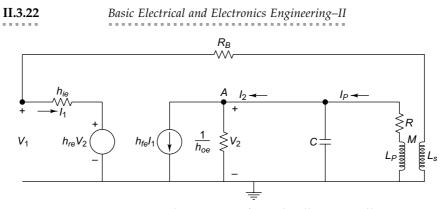

- 3.10 Tuned Collector Oscillator II.3.20

- 3.11 Tuned LC Oscillators II.3.24

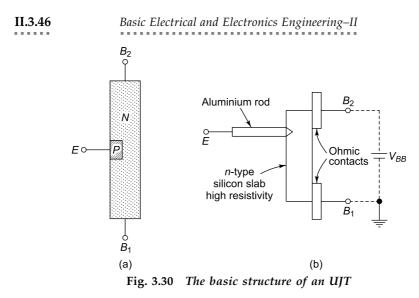

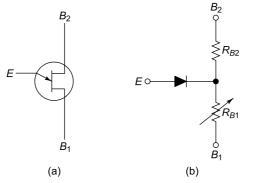

3.12 Crystal Oscillators II.3.36 Exercises II.3.39 Multiple Choice Questions II.3.41

- University Questions with Answers II.3.44

#### 4. Operational Amplifier

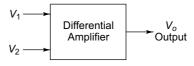

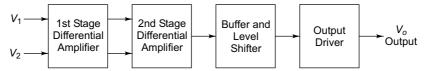

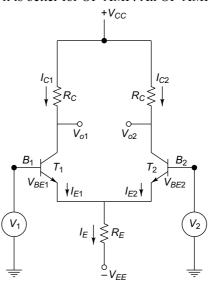

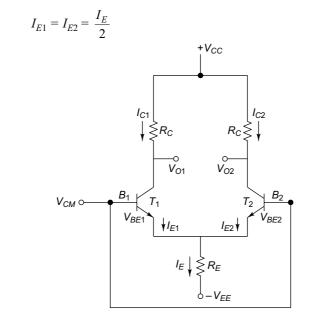

- 4.1 Introduction *II.4.1*

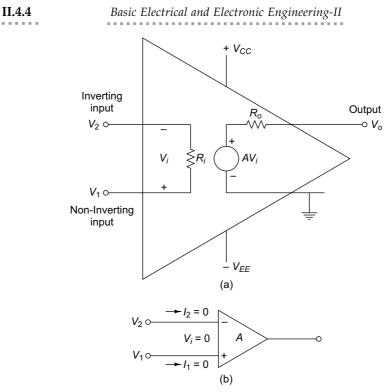

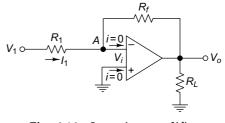

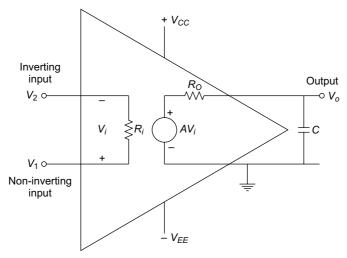

- 4.2 The Ideal OP-AMP II.4.3

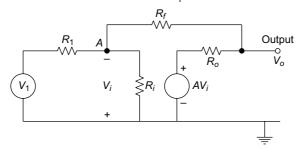

- 4.3 Equivalent Circuit of an OP-AMP II.4.3

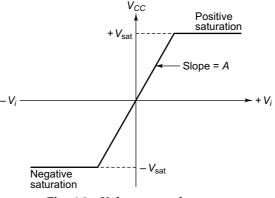

- 4.4 Ideal Voltage Transfer Curve II.4.5

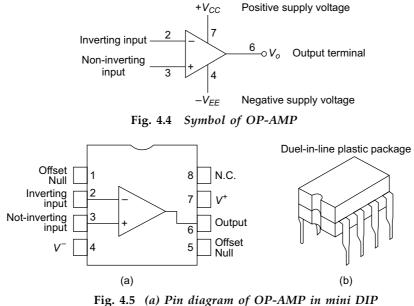

- 4.5 OP-AMP Symbol and Terminals *II.4.5*

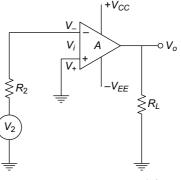

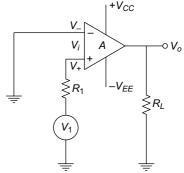

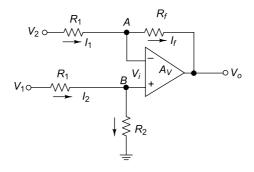

- 4.6 Difference Amplifier II.4.6

#### II.4.1–II.4.47

II.3.1–II.3.48

II.2.1-II.2.62

ix

| x                                  | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

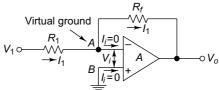

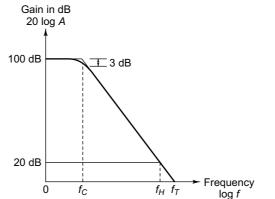

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.8<br>4.9<br>4.10<br>4.11<br>4.12 | <ul> <li>Operational Amplifier Internal Circuit <i>II.4.10</i></li> <li>Open-loop Configurations of OP-AMP <i>II.4.15</i></li> <li>Feedback in Ideal OP-AMP <i>II.4.17</i></li> <li>OP-AMP Characteristics <i>II.4.22</i></li> <li>Virtual Ground <i>II.4.32</i></li> <li>Frequency Response of Operational Amplifier <i>II.4.35</i></li> <li>Stability of Operational Amplifier <i>II.4.35</i></li> <li><i>Exercises II.4.36</i></li> <li>Multiple Choice Questions <i>II.4.39</i></li> </ul> |                |

|                                    | University Questions with Answers II.4.41                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

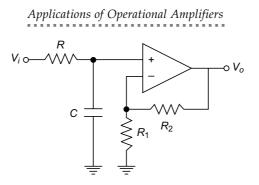

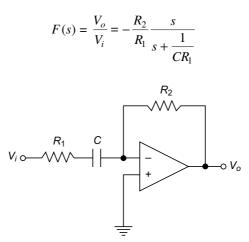

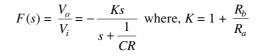

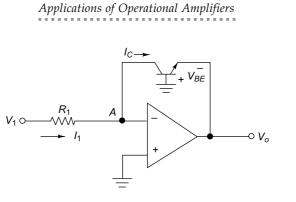

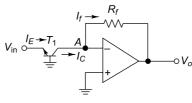

| 5. Apj                             | plications of Operational Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                           | II.5.1–II.5.69 |

| 5.1                                | TIntroduction II.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

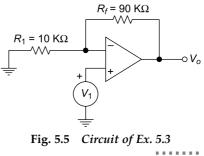

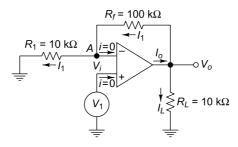

| 5.2                                | 2 Inverting Amplifier <i>II.5.2</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

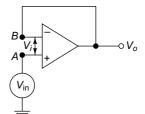

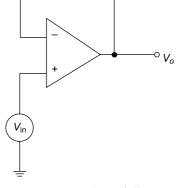

|                                    | B Non-inverting Amplifier <i>II.5.3</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|                                    | Voltage Follower <i>II.5.5</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

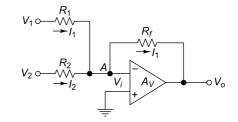

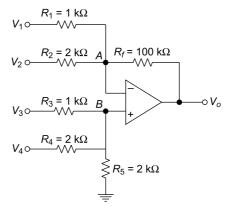

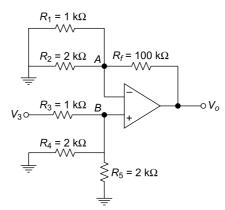

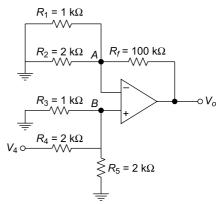

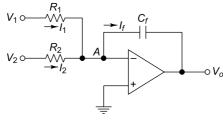

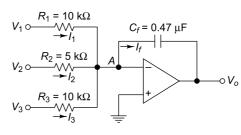

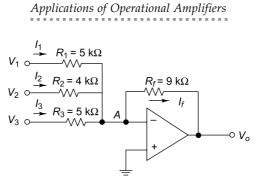

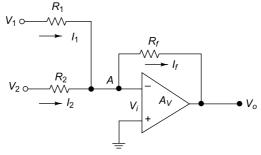

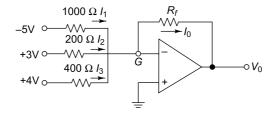

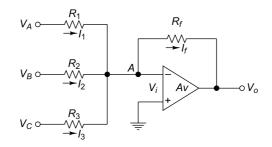

|                                    | 5 Adder or Summing Amplifier <i>II.5.6</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

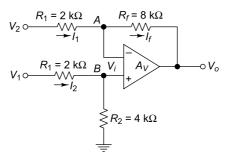

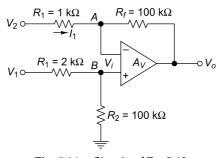

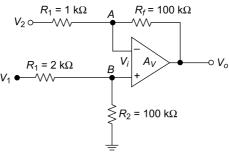

|                                    | 5 Subtractor or Difference Amplifier <i>II.5.10</i>                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|                                    | Difference Amplifier with one OP-AMP <i>II.5.11</i>                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

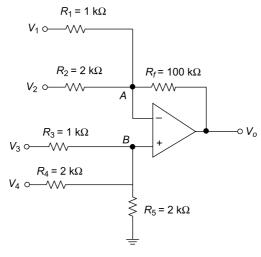

|                                    | Adder–Subtractor <i>II.5.12</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

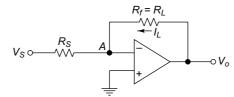

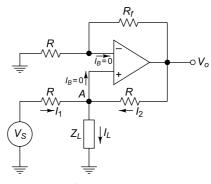

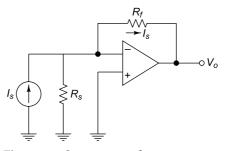

|                                    | Voltage-to-current Converter <i>II.5.18</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|                                    | Current-to-voltage Converter <i>II.5.19</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

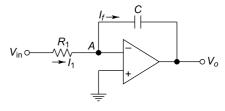

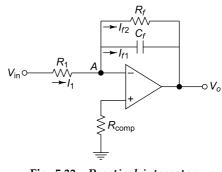

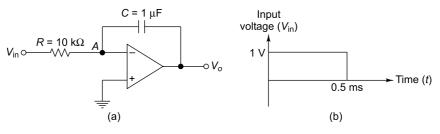

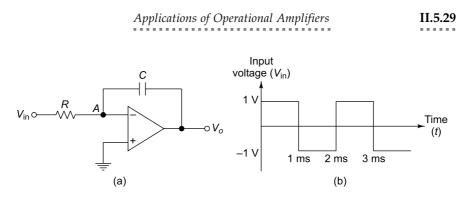

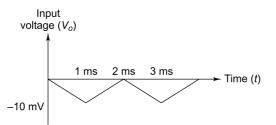

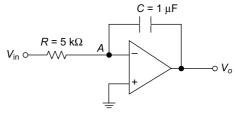

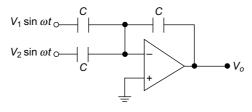

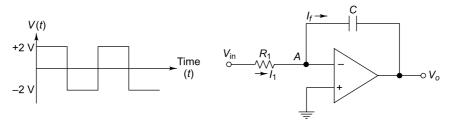

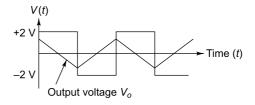

|                                    | Integrator 11.5.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

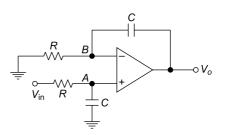

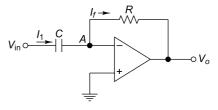

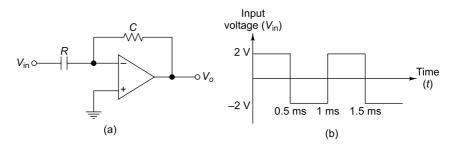

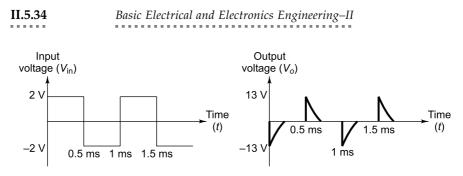

|                                    | 2 Differentiator <i>II.5.30</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

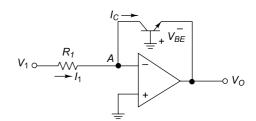

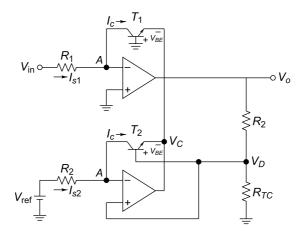

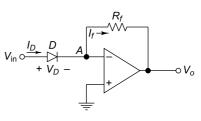

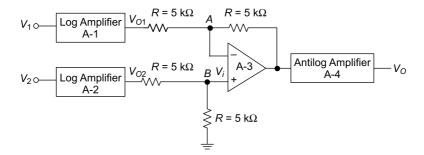

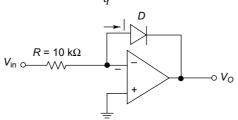

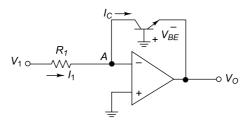

|                                    | 3 Logarithmic Amplifier <i>II.5.34</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

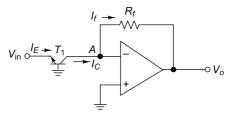

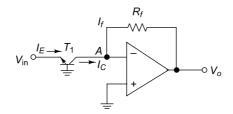

|                                    | Antilog Amplifier <i>II.5.37</i><br>Antilog Amplifier Using Transistor <i>II.5.38</i>                                                                                                                                                                                                                                                                                                                                                                                                          |                |

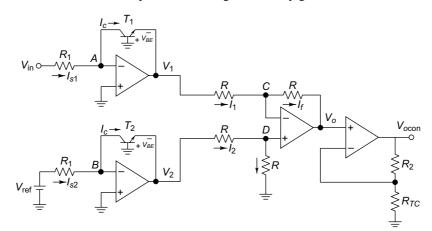

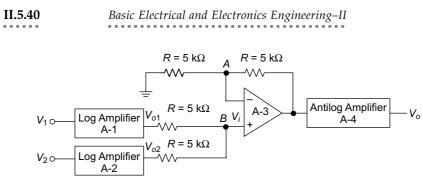

|                                    | 6 Analog Multiplier <i>II.5.39</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|                                    | Analog Divider II.5.41                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

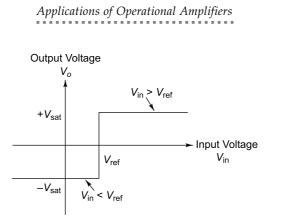

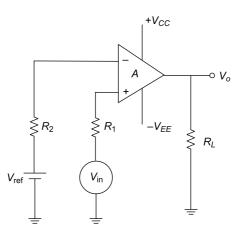

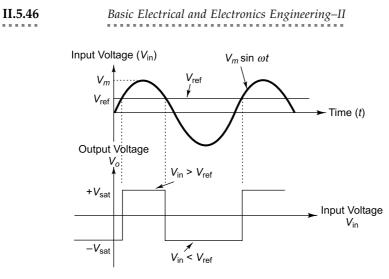

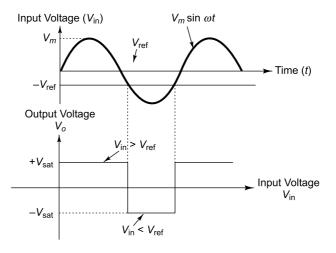

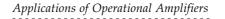

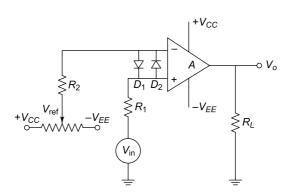

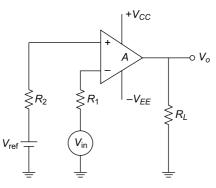

|                                    | B Comparator <i>II.5.44</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

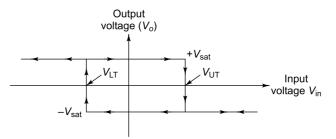

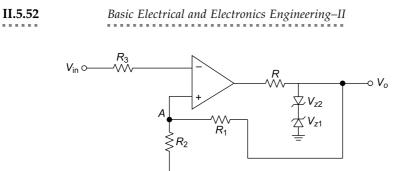

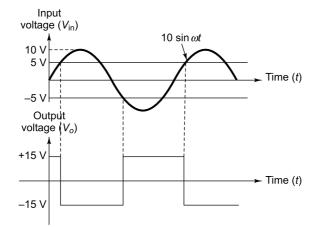

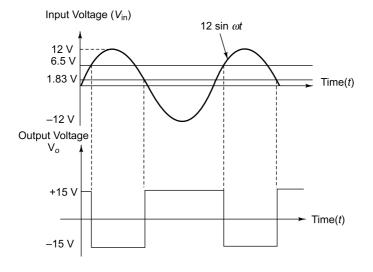

|                                    | Schmitt Trigger <i>II.5.49</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                                    | Realization of Functions using OP-AMP <i>II.5.54</i>                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| 5.20                               | Exercises II.5.57                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|                                    | Multiple Choice Questions II.5.62                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|                                    | University Questions with Answers II.5.65                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| 6. Nu                              | nber System, Boolean Algebra and Logic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                | II.6.1–II.6.54 |

|                                    | Introduction II.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|                                    | 2 Number Systems <i>II.6.2</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                                    | B Binary Arithmetic II.6.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|                                    | Binary Coded Decimal (BCD) Number System <i>II.6.17</i>                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 6.4                                | 5 Boolean Algebra II.6.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

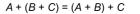

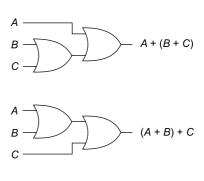

- 6.5 Boolean Algebra *II.6.1*6.6 Boolean Laws *II.6.20*

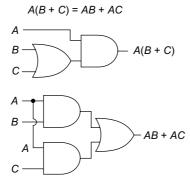

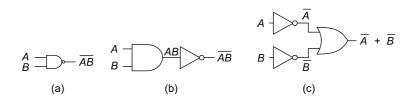

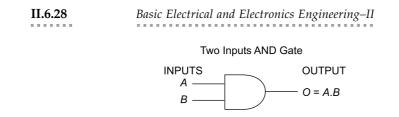

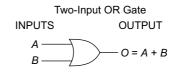

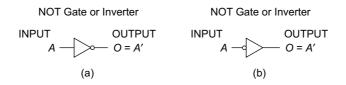

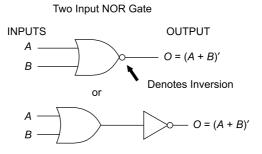

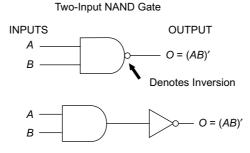

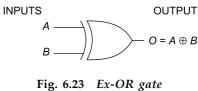

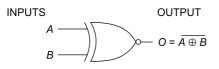

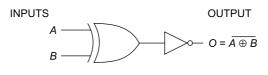

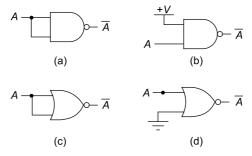

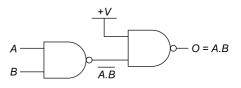

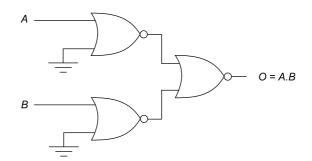

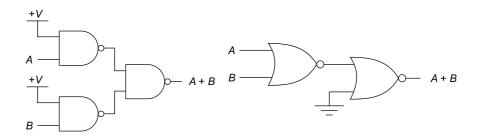

- 6.7 De Morgan's Theorem *II.6.25*6.8 Logic Gates *II.6.27*

| 6.9    | Universal Gate 11.6.32                |                    |

|--------|---------------------------------------|--------------------|

| 6.10   | Digital Logic Circuits <i>II.6.36</i> |                    |

|        | Exercises II.6.50                     |                    |

|        | Multiple Choice Questions II.6.52     |                    |

|        | Answers to MCQ's II.6.54              |                    |

| Solved | WBUT Question Paper (2012)            | II.SQP.1–II.SQP.9  |

| Solved | WBUT Question Paper (2013)            | II.SQP.1–II.SQP.5  |

| Solved | WBUT Question Paper (2014)            | II.SQP.1–II.SQP.6  |

| Solved | WBUT Question Paper (2015)            | II.SQP.1–II.SQP.10 |

|        |                                       |                    |

Contents

xi

# PREFACE

Basic Electrical Engineering and Basic Electronics Engineering are the two fundamental subjects of most engineering disciplines. It is extremely important to ensure that the fundamentals of these two courses are well understood by all engineering students since these subjects have applications in all streams. Though numerous textbooks on these two subjects are already available, we felt that there was still a need for another book which would present the basics of Electrical and Electronics Engineering in a comprehensive manner. It is also true that there is hardly any comprehensive textbook available on this subject that precisely covers the prescribed syllabus of WBUT. Moreover, following the new syllabus framed by West Bengal University of Technology (WBUT), there was a need to bring out a textbook that would cover the entire syllabus of Basic Electrical and Electronics Engineering-II. An attempt has, therefore, been made to present an exhaustive material in the form of a textbook to the students studying basic electrical and electronics engineering in WBUT. We hope that after going through this book, the undergraduate engineering students of WBUT will find that their learning and understanding of the subject, Basic Electrical and Electronics Engineering, has increased progressively.

Our main aim was to equip the students with the fundamental knowledge of Electrical and Electronics Engineering, the theory backed up by illustrative solved problems. We have emphasized on building of fundamental concepts, mathematical derivations coupled with applications and solutions of problems. We have attempted to keep the language in the textbook as lucid as possible. Relevant examples have been selected to supplement the theory so that students have a thorough idea of the applicability of the theoretical concepts. The salient features of this book are as follows:

- · Coverage and chapter organization as per the syllabus of WBUT

- Important statements and key terms highlighted within the topics for better clarity

- Individual topics are very well supported by the solved examples

- Single book containing the fundamentals of both electrical and electronics engineering

- · Stepwise explanation of theories and derivations along with relevant examples

- Diagrammatic and elaborate representation of circuits and phasors

- Numerous solved examples and adequate exercise problems for practice

- Solutions of WBUT previous year questions from 2003–2015 incorporated within the book appropriately.

Preface

• Pedagogy includes:

-507 Solved Examples -347 Practice Questions with Answers -224 Multiple Choice Questions -589 Illustrations

The book comprises 12 chapters designed as per WBUT syllabus. The first six chapters deal with the fundamentals of basic electrical engineering, and the next six chapters deal with the fundamentals of basic electronics engineering.

Part I is organized in six chapters as follows:

**Chapter 1** deals with electrostatics with emphasis on Coulomb's law, Gauss's law, electric field intensity and capacitance.

**Chapter 2** introduces dc machines and presents the concepts of magnetic flux, equivalent circuit, back emf, armature windings, speed-torque characteristics and applications of dc machines.

**Chapter 3** describes single-phase transformers, their construction, operation, regulation and efficiency.

Chapters 4 and 5 introduce three-phase systems and three-phase induction motors respectively.

**Chapter 6** presents the structure of a power system with special emphasis on distribution and representation.

The second part of Basic Electrical and Electronics Engineering is written as a first course of electronics, incorporating both analog and digital electronics devices and circuits. This part of the book allows students to achieve an enhanced level of understanding within the prescribed period and helps them develop a strong foundation for other electronics specialized courses. The principles of operation of various devices are explained properly, and examples and solved problems ranging from simple to complex have been incorporated. After studying this book, we are sure students can perform better in semesters as well as in competitive examinations.

Part II aims to provide working knowledge about analog and digital logic elements and the expertise required to develop analog and digital systems. This part covers the following areas: field effect transistors, feedback amplifier and oscillators, operational amplifier, number system, and Boolean algebra.

Part II is organized into six chapters as explained below:

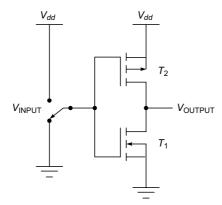

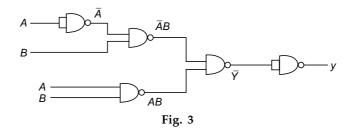

**Chapter 1** describes the basic concept of field effect transistors, JFET structure and its characteristics, MOSFET structure and characteristics, depletion and enhancement-type MOSFET, common source, common gate and common drain configuration of FET, and basic principles of CMOS.

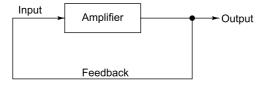

**Chapter 2** presents the basic concept of positive and negative feedback amplifiers, classification of amplifiers, different topologies of feedback amplifiers, and properties of feedback amplifiers.

**Chapter 3** describes the basic concept of oscillators, Barkhausen criteria, classification of oscillators, phase-shift oscillation, Wein bridge oscillator, tuned collector oscillator, LC oscillators, Colpitts, Hartley and crystal oscillators.

xiv

| 1 | P  | re | fi | a  | Ce | , |

|---|----|----|----|----|----|---|

|   | н. | н. | н. | н. | н. | н |

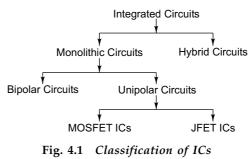

**Chapter 4** is related to operational amplifiers. The integrated circuits, ideal OP-AMP, equivalent circuit of OP-AMP, difference amplifier, configuration of OP-AMP, characteristics, frequency response and stability of OP-AMP and the concept of virtual ground are discussed elaborately in this chapter.

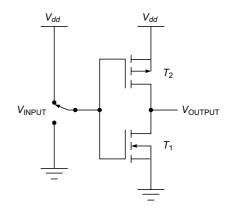

**Chapter 5** deals with design and implementation of analog circuits using an operational amplifier. The application of operational amplifiers in adder, subtractor, voltage-to-current converter, current-to-voltage converter, multiplier, voltage follower, integrator, differentiator, logarithmic amplifier, multiplier, divider and Schmitt trigger are incorporated in this chapter.

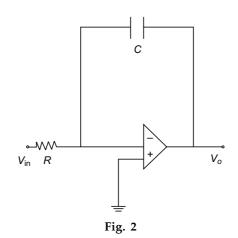

**Chapter 6** provides the basic concepts of number systems, binary arithmetic, BCD codes, Boolean algebra and various logic operations. The correlation between Boolean expressions and implementation using logic gates is explained. The operation of logic gates with logic diagrams, De Morgan's theorems, and simplification of logic circuits are also incorporated.

Care has been taken regarding the chronology of presentations, mathematical treatments and in representing the theory in a lucid manner. Each chapter has sufficient number of theoretical questions and unsolved problems with hints and answers. For the benefit of students, we have also included answers of questions and detailed solutions of problems from question papers of WBUT.

#### Acknowledgements

A number of experts took pains to provide valuable feedback on various chapters of the book. Our heartfelt gratitude goes out to those whose names are given below:

| Sayantan Chakraborty     | Dr. Sudhir Chandra Sur Degree Engineering<br>College, Kolkata |

|--------------------------|---------------------------------------------------------------|

| Chandra Monli Gupta      | Adamas Institute of Technology, Kolkata                       |

| Subhra Mukherjee         | Narula Institute of Technology, Kolkata                       |

| Goutam Das               | Haldia Institute of Technology, Medinipur                     |

| Chameli Sarkar           | Sir J C Bose School of Engineering, Nadia                     |

| <b>Rabindranath Shaw</b> | Brainware Institute of Technology, Kolkata                    |

| D Lahiri                 | Techno India Group, Kolkata                                   |

| G S Taki                 | Institute of Engineering and Management (IEM),<br>Kolkata     |

| Sudip Dogra              | Meghnad Saha Institute of Technology, Kolkata                 |

| Shila Ghosh              | B P Poddar Institute of Management and Technology,<br>Kolkata |

| Asim Kar                 | Academy of Technology, Kolkata                                |

| Sucharita Ghosh          | Future Institute of Engineering and Management,<br>Kolkata    |

xv

Preface

We acknowledge the assistance and encouragement of all our colleagues and staff.

Soumitra Kumar Mandal would like to acknowledge the sincere cooperation and inspiration that he received from Dr Gurnam Singh, PEC, Chandigarh; Dr S Chatterjee, NITTTR, Chandigarh; Dr S K Bhattachariya, Director NITTTR, Kolkata; Prof. Amitabha Sinha, Director School of IT, WBUT; Dr P Shyam, Bengal Engineering College, Shibpur; Dr P Sarkar, Professor and Head, Electrical Engineering; Dr S Chattopadhay, Associate Professor; and Dr S Pal, Assistant Professor, NITTTR, Kolkata. He is also thankful to other staff of Electrical Engineering—Mr A K Das, Mr N K Sarkar, Mr S Roy Choudhury, and Mr Surojit Mallick—who helped him complete the manuscript of this book.

We are also very thankful to our family members for their continuous support, encouragement and patience throughout the writing of the manuscript of this book.

We express sincere gratitude to the entire team of McGraw Hill Education (India) in bringing out this book in a very short time. We will be extremely thankful to the readers for their constructive suggestions and views to enhance the utility of this book.

Abhijit Chakrabarti Sudipta Debnath Soumitra Kumar Mandal

#### Publisher's Note

**Remember to write to us.** We look forward to receiving your feedback, comments and ideas to enhance the quality of this book. You can reach us at *info.india@mheducation.com*. Kindly mention the title and the author's name as the subject. In case you spot piracy of this book, please do let us know.

xvi

# **ROADMAP TO THE SYLLABUS**

# BASIC ELECTRICAL AND ELECTRONICS ENGINEERING-II

This text is suitable for the Paper Code ES201.

# PART I: BASIC ELECTRICAL ENGINEERING-II

**Electrostatics**: Coulomb's law; Electric field intensity; Electric field due to a group of charges; Continuous charge distribution; Electric flux; Flux density; Electric potential; Potential difference; Gauss's law; Proof of Gauss's law and its applications to electric field and potential calculation; Capacitor; Capacitance of parallel plate capacitor; Spherical capacitor; Isolated spheres; Concentric conductors; Parallel conductors; Energy stored in a capacitor

# **CHAPTER 1: ELECTROSTATICS**

**DC Machines:** Construction; Basic concepts of winding (lap and wave); dc generator—principle of operation, emf equation, characteristics (open circuit, load); dc motors—principle of operation; speed—torque characteristics (shunt and series machine); Starting (by 3-point starter); Speed control (armature voltage and field control)

#### **CHAPTER 2: DC MACHINES**

**Single-phase Transformer:** Core and shell-type construction; emf equation; Noload and on-load operation; Phasor diagram and equivalent circuit; Losses of a transformer; Open and short-circuit tests; Regulation and efficiency calculation

**Three-phase Induction Motor:** Types; Construction; Production of rotating field; Principle of operation; Equivalent circuit and phasor diagram; Rating; Torque–

Roadmap to the Syllabus

speed characteristics (qualitative only); Starter for squirrel-cage and wound-rotor induction motor; Brief introduction of speed control of three-phase induction motor (voltage control; frequency control; resistance control)

**General Structure of Electrical Power System:** Power generation to distribution through overhead lines and underground cables with single lone diagram

CHAPTER 6: STRUCTURE OF A POWER SYSTEM

**Three-phase System:** Voltages of three balanced phase systems; Delta and star connection; Relationship between line and phase quantities; Phasor diagrams; Power measurement by two-wattmeter method

Go to

Go

CHAPTER 4: THREE-PHASE SYSTEM

# PART II: BASIC ELECTRONICS ENGINEERING-II

**Field Effect Transistors:** Concept of field Effect Transistors (channel width modulation); Gate isolation types; JFET structure and characteristics; MOSFET structure and characteristics; Depletion and enhancement types; CS, CT, CD configurations; CMOS: basic principles

**CHAPTER 1: FIELD EFFECT TRANSISTORS**

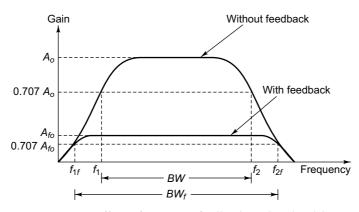

**Feedback Amplifiers and Oscillators:** Concept (block diagram); Properties; Positive and negative feed back; Loop gain; Open loop gain; Feedback factors; Topologies of feedback amplifier; Effect of feedback on gain; Output impedance; Input impedance; Sensitivities (qualitative); Bandwidth stability; Effect of positive feedback—instability and oscillation; condition of oscillation; Barkhausen criteria

CHAPTER 2: FEEDBACK AMPLIFIER CHAPTER 3: OSCILLATORS

xviii

**Operational Amplifier:** Introduction to integrated circuits; Operational amplified and its terminal properties; Application of operational amplifier; Inverting and non-inverting mode of operation; Voltage summing and difference; Constant gain multiplier; Voltage follower; Comparator; Integrator; Differentiator; Schmitt trigger; Logarithmic amplifier

#### CHAPTER 4: OPERATIONAL AMPLIFIER CHAPTER 5: APPLICATIONS OF OPERATIONAL AMPLIFIERS

**Introduction to Digital Electronics:** Introduction to binary number; Basic Boolean algebra; Logic gates; and function realization with OP-AMPs

#### CHAPTER 6: NUMBER SYSTEM, BOOLEAN ALGEBRA AND LOGIC CIRCUITS

# ELECTROSTATICS

# **1.1 INTRODUCTION**

In *electrostatics* we deal with static electricity (i.e, when charges are at rest). The knowledge of electrostatics is important in electrical engineering as we frequently come across the design process of electrical insulations and performance of various equipment, cables and overhead lines when subjected to electric stress. Natural phenomenon like lightning is very much related to electrostatic processes and laws. Electrostatics finds extensive applications in extra high voltage systems (ehv) in transmission engineering. *Capacitors* play a vital role in different spheres of electrical engineering as well as electronics engineering. The performance of a capacitor can be best analysed and it can be properly designed with knowledge in electrostatics.

### 1.2 COULOMB'S LAW

*Coulomb's first law* states that like charges repel each other while opposite charges attract each other. *Coulomb's second law* states that the force of attraction between two opposite charges or force of repulsion between two like charges is

- (a) directly proportional to the product of the charges, the distance between them being same;

- (b) inversely proportional to the square of the straight distance between them, magnitude of the charges being constant.

If we assume the charges to be of magnitude (Q) and (q) separated by a straight distance x, then from Coulomb's second law we can write

$F \propto Q \times q/x^2$ , (F) being the force of repulsion if both charges are alike or force of attraction if the charges have opposite polarity. The force (F) is measured in Newtons when the magnitude of the charges are expressed in Coulombs and the distance in meters.

$$F = K \frac{Q \cdot q}{x^2} \tag{1.1}$$

# I.1.2 Basic Electrical and Electronics Engineering–II

(*K*) being constant of variation and in SI unit (*K*) in vacuum is given by  $1/4\pi\varepsilon_o$ ; otherwise  $K = 1/4\pi\varepsilon$ , when the charges are placed in any other medium other than vacuum or space.

$$\therefore \qquad F = \frac{Q \cdot q}{4\pi\varepsilon x^2} \tag{1.2}$$

In electrical engineering we term this  $\varepsilon$  as permittivity of the medium in which charges are placed. It is known as absolute permittivity and is represented as

$$\varepsilon = \varepsilon_o \times \varepsilon_r \tag{1.3}$$

where  $(\varepsilon_o)$  is the *permittivity* of space while  $(\varepsilon_r)$  is the *relative permittivity* of the medium where the charges are placed. In SI unit,

$\varepsilon_o = 8.854 \times 10^{-12}$  Farad/metre

$$\therefore \qquad \frac{1}{4\pi\varepsilon_o} = \frac{1}{4\pi \times 8.854 \times 10^{-12}} = 9 \times 10^9$$

Thus, Coulomb's law can be written as

$$F = 9 \times 10^9 \ \frac{Q \times q}{\varepsilon_r x^2} \,. \tag{1.4a}$$

When the charges are placed in vacuum (or space),

$$F = 9 \times 10^9 \frac{Q \cdot q}{x^2}$$

. (1.4b)

If Q = q = 1 Coulomb and x = 1 metre, from Coulombs law,  $F = 9 \times 10^9$  Newtons (in space). This gives rise to the definition of *unit charge* (i.e. 1 Coulomb) which means that it is such a charge which when placed at one metre apart from another similar charge experiences a force of  $9 \times 10^9$  Newton in vacuum.

#### **1.3 PERMITTIVITY**

Permittivity of a medium is basically that property of the medium which permits electric flux to pass through it. If the permittivity is more it means that the medium allows more flux to pass through it and hence this medium is more susceptible to the electric field.

Absolute permittivity ( $\varepsilon$ ) is the ratio of electric flux density in a dielectric medium to the corresponding electric field strength and is expressed as Farad/meter.

i.e

$$\varepsilon = \frac{\delta}{E} \text{ F/m}$$

(1.5)

where  $\delta$  is electric flux density and *E* is the strength of the field.

Also,  $\varepsilon = \varepsilon_o \times \varepsilon_r$ , where  $\varepsilon_o$  is the permittivity of free space (8.854 × 10<sup>-12</sup> F/m) and ( $\varepsilon_r$ ) is the relative permittivity of a dielectric medium. It is defined as the ratio of flux densities of the dielectric medium to that in vacuum produced by the same electric field strength.

Electrostatics

$$[e_r = \frac{\delta}{\delta_o} = \frac{(\varepsilon E)}{(\varepsilon_o E)} = \frac{\varepsilon}{\varepsilon_o}$$

$\therefore \qquad \varepsilon = \varepsilon_r \times \varepsilon_0$ ]

Relative permittivity of space is 1 while that of air is 1.0006. In practice, we assume  $\varepsilon_r$  of vacuum and air as 1. Commonly used dielectric medium have permittivity between 2 and 10.

#### 1.4 ELECTRIC FLUX AND FLUX DENSITY

*Electric flux* represents the total number of lines of force in any electric field. It is the lines of force coming out of a positive charge of one coulomb. Electric flux is often represented by symbol  $\psi$  or  $\phi$  and expressed in Coulombs.

Electric flux density (often represented by the sysmbol  $\delta$ ) may be defined as the flux per unit area, measured at right angles to the direction of electric flux. Its unit is Coulomb per sq. metre.

i.e.,  $d = \frac{\phi}{A} e/m^2$ , where A represents the area in m<sup>2</sup>.

# 1.5 ELECTRIC POTENTIAL AND POTENTIAL DIFFERENCE

The *electric potential* at any point in an electric field is defined as the work done in joules in moving a unit positive charge from infinity (i.e., from zero potential) to that point against the electric field.

$$\therefore \qquad \text{Electric potential} = \frac{\text{Work done}}{\text{Electric charge}}$$

or

$$V = \frac{W}{Q} \tag{1.6}$$

When W is expressed in joules, Q in coulombs, V is expressed in volts. Then the electric potential at a particular point in an electric field is one volt provided one joule of work is done in moving a unit positive charge from zero potential to that point against the field.

In electrical engineering we are more interested in measuring the potential difference between two points in a field than to know the absolute value of the electric potential at any point s in the field. The *potential difference* (p.d.) is the work done in joule in moving a unit positive charge from the point of lower potential to higher potential within the field.

The potential difference is obviously measured in volts and the p.d. of one volt means one joule of work is done in bringing a unit positive charge from the point of lower potential to the point of higher potential within the electric field.

I.1.3

### I.1.4 Basic Electrical and Electronics Engineering–II

# 1.6 EXPRESSION FOR POTENTIAL AT A POINT WITHIN AN ELECTRIC FIELD

Let us consider two positive charges, the first one having a charge of Q coulombs while the second one is a unit positive charge. Both the charges are assumed to be placed in space at a straight distance x metres between them. From Coulomb's law we can express the force of repulsion between these two charges as

$$F = \frac{Q \times 1}{(4\pi\varepsilon_o)x^2}$$

;  $\varepsilon_o$  being the permittivity of space.

The work done dW in moving the unit charge towards the charge Q for a small distance dx metre will be given as

$$dW = \left[\frac{Q}{(4\pi\varepsilon_o)x^2}(-dx)\right] \text{ joule}$$

Work done is negative as the charge is moved against a repulsive force and against the direction of the field.

In order to find the total work done in moving the unit positive charge from infinity to any point d metres away from the charge Q against the field, we will integrate the expression of dW obtained within the limit of integral  $\infty$  to d.

$$\therefore \qquad W = \int_{\infty}^{d} \frac{Q(-dx)}{(4\pi\varepsilon_o)x^2} = \frac{-Q}{4\pi\varepsilon_o} \left[ -\frac{1}{x} \right]_{\infty}^{d} = \frac{Q}{(4\pi\varepsilon_o) \cdot d} \text{ joules}$$

Thus, from definition we can write the potential at a point d metres away from the

charge

$$Q$$

is simply  $\left(\frac{Q}{4\pi\varepsilon_o \cdot d}\right)$  volts.

$$\therefore \qquad V = \frac{Q}{(4\pi\varepsilon_o) \cdot d} \text{ volts} \qquad (1.7a)$$

If the analysis be performed assuming the surrounding medium as a dielectric of relative permitivity  $\varepsilon_r$ , we can modify the expression for potential at distance *d* away from *Q* as

$$V = \frac{Q}{4\pi\varepsilon_o\varepsilon_r \cdot d} \text{ volts}$$

(1.7b)

If we consider an isolated sphere of radius R placed in space and having +ve charge Q coulombs uniformly distributed over its surface, the potential at the surface of the sphere would be

$$V = \frac{Q}{4\pi\varepsilon_o R} \tag{1.8}$$

[the charge on the sphere would act as a concentrated charge at the centre O of the sphere.]

| Electrostatics | I.1.5 |

|----------------|-------|

|                |       |

The potential will remain constant for the space between O and R in the sphere and will be same as the potential V at the surface of the sphere. The surface of the sphere would be termed as equipotential surface and electric lines of force always cross such a equipotential surface normally. If we assume a point P outside the sphere at distance D from the centre of the sphere, we would have the potential of  $V_P = Q/(4\pi\epsilon_0 D)$  at that point outside the sphere.

## **1.7 ELECTRIC FIELD INTENSITY**

The *intensity of the electric field* at a point is defined as the mechanical force per unit charge placed at that point. The direction of the intensity is same as direction of the force exerted on a positive charge.

Thus, if F be the force experienced by a test charge q placed at a point in an electric field, the intensity E at that point is given by

$$E = \frac{F}{q} \,. \tag{1.9}$$

*E* is expressed in newton per coulomb or in volt/metre (V/m). Frequently the term *electric field strength* is also used in-

stead of the term electric field intensity.

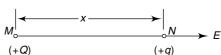

Let us assume a positive point charge +Q is placed at a point M and a test charge +q is placed at point N, as shown in Fig. 1.1.

Fig. 1.1 A (+ve) charge (+Q) placed in an electric field

The force F experienced by q is given by

$$F = \frac{Qq}{4\pi\varepsilon_o x^2} \,.$$

Since intensity E is given by F/q, we can write

$$E = \frac{Q}{4\pi\varepsilon_o x^2} \,. \tag{1.10}$$

The direction of E is towards the point charge or away from it according as the charge is negative or positive.

# **1.8 ELECTRIC FIELD INTENSITY AND** POTENTIAL OF ISOLATED POINT CHARGE (Q) +q

Figure 1.2 represents an isolated point charge +q placed F in space. We are to find the field intensity and potential at point *P*.

Fig. 1.2 An isolated point charge (+q) placed in space

Ť

#### Basic Electrical and Electronics Engineering–II

To find intensity:

By definition of electric field intensity, the intensity at a point is given by (in vector form)

$$E = \frac{1}{4\pi\varepsilon_o} \times \frac{q}{r^2} \tag{1.11a}$$

where q = positive point charge

r = distance between +q and point P and

$\varepsilon_0$  = permittivity of space

To find potential:

By definition of potental at a point P,

$$V = -\int_{-\infty}^{r} |\vec{E}| dr = -\int_{-\infty}^{r} \frac{1}{4\pi\varepsilon_{o}} \left(\frac{q}{r^{2}}\right) dr = -\left[-\frac{1}{4\pi\varepsilon_{o}} \left(\frac{q}{r}\right) - 0\right] = \frac{q}{4\pi\varepsilon_{o}r}$$

$$V = \frac{q}{4\pi\varepsilon_{o}r}.$$

(1.11b)

### **1.9 POTENTIAL DUE TO A GROUP OF CHARGES**

The potential at a point due to a number of charges can be determined by algebraically adding the potential at that point due to each one of the charges. Let  $q_1, q_2, q_3, \ldots$  be the charges at distances  $r_1, r_2, r_3 \ldots$  respectively from a given point *P* at which we are required to find the resultant of the above charges. The resultant potential (*V*) is then given by

$$V = \frac{q_1}{4\pi\varepsilon_0\varepsilon_r r_1} + \frac{q_2}{4\pi\varepsilon_0\varepsilon_r r_2} + \frac{q_3}{4\pi\varepsilon_0\varepsilon_r r_3} + \dots$$

$$V = \frac{q}{4\pi\varepsilon_0\varepsilon_r} \left[ \frac{1}{r_1} + \frac{1}{r_2} + \frac{1}{r_3} + \dots \right]$$

(1.12)

(assuming  $q_1 = q_2 = q_3 = ... = q$ )

# 1.10 ELECTRIC FIELD INTENSITY AND POTENTIAL GRADIENT

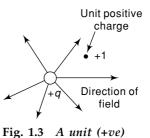

Electric field strength E due to a point charge at any point in the vicinity of the charge is defined as the force experienced by a unit positive charge placed at that point within the field (Fig. 1.3). It is expressed in Newton/Coulomb (or volt/meter). If this force is stronger, the electric field strength is more. We also can state that the work done in moving a unit positive charge through a small distance dx meters in the direction of the field is given by

charge in a field

I.1.6

*.*•.

or,

(dW) =force  $\times$  displacement of the charge

=  $E \times dx$  joules, where E is expressed in Newton/Coulomb.

Obviously this work done would be equal to the "drop" or reduction in potential as this time the unit positive charge is moved along the direction of the field and the work done would consequently be positive.

Then we can write  $dV = E \times dx$

or

$$E = \frac{dV}{dx}$$

(1.13)

(dV/dx) is known as the *potential gradient* and is thus the drop in potential per meter in the direction of the field. It is expressed as volt/meter. We thus find that the electric field strength and potential gradient being same, both are expressed in volt/meter.

## 1.11 RELATION BETWEEN ELECTRIC FLUX DENSITY AND ELECTRIC FIELD INTENSITY

We have just derived

or

$$E = \frac{Q}{4\pi\varepsilon_0\varepsilon_r r^2} = \frac{Q}{4\pi\varepsilon r^2}$$

i.e.,

The quantity  $\varepsilon E$  has dimensions of charge per unit area and is equivalent to electric flux density (d).

$$\therefore \qquad d = \varepsilon E = \frac{Q}{4\pi r^2} \tag{1.14}$$

# 1.12 ELECTRIC POTENTIAL ENERGY

$\varepsilon E = \frac{Q}{4\pi r^2}$

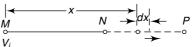

Let us consider a system of two charges  $Q_1$ and  $Q_2$ . Suppose  $Q_1$  is a fixed charge at a point *M* while the charge  $Q_2$  is taken from a point *N* to a point *P* along the line MNP (Fig. 1.4).

Let distance  $MN = x_1$ , while distance  $MP = x_2$ . We consider a small displacement of charge  $Q_2$ . Its distance from M then changes to (x + dx). The electric force on  $Q_2$  is given by

$$F = \frac{Q_1 Q_2}{4\pi\varepsilon_o x^2}$$

, in direction *M* to *N*.

[We assume the medium in which the charges are placed in space and hence  $\varepsilon_r = 1$ ]

I.1.7

### Basic Electrical and Electronics Engineering–II

The work done by the force in making small displacement dx by the charge is

$$dW = \frac{Q_1 Q_2}{4\pi\varepsilon_o x^2} \cdot dr$$

[:: Work done = force × displacement] The total work done as  $Q_2$  moves from N to P is thus

$$W = \int_{x_1}^{x_2} \frac{Q_1 Q_2}{4\pi\varepsilon_o x^2} \cdot dx$$

$$= \frac{Q_1 Q_2}{4\pi\varepsilon_o} \left[ \frac{1}{x_1} - \frac{1}{x_2} \right] \text{ joule}$$

(1.15)

[Charges are expressed in Coulomb and distance in metres] [It may be noted here that no work is done by the electric force on the charge  $Q_1$  as it remains fixed.]

The change in potential energy is thus

$$u(x_{2}) - u(x_{1}) = -W = -\frac{Q_{1}Q_{2}}{4\pi\epsilon_{o}} \left[\frac{1}{x_{1}} - \frac{1}{x_{2}}\right]$$

$$= \frac{Q_{1}Q_{2}}{4\pi\epsilon_{o}} \left[\frac{1}{x_{2}} - \frac{1}{x_{1}}\right]$$

(1.16)

[We define *change in electric potential energy* of the system as negative of work done by the electric force.]

If one charge is placed at infinity, its potential is zero and consequently  $u(\infty) = 0$ . The potential energy, when the separation is *x*, can be obtained as

$U(x) = u(x) - u(\infty)$

$$= \frac{Q_1 Q_2}{4\pi\varepsilon_o} \left(\frac{1}{x} - \frac{1}{\infty}\right) = \frac{Q_1 Q_2}{4\pi\varepsilon_o x}$$

(1.17)

The equations derived here assume that one of the charges is fixed and the other is moving. However, the potential energy depends essentially on the separation between charges and is independent of the spatial location of the charged particles.

# 1.13 RELATION BETWEEN ELECTRIC FIELD STRENGTH AND POTENTIAL

Let us suppose the electric field at a point *n* due to a charge distribution is *E*, while the electric potential at the same point is *V*. Let us assume the point charge of strength *q* is moved slightly from the point *x* to (x + dx). The force on the charge is  $F = q \times E$ , while the work done is

$$dW = F(-dx) = qE(-dx)$$

I.1.8

[In article 1.8, we have assumed dx in the direction of the field, i.e. from +q towards infinity. If any charge is moved against the field, dx becomes –ve.] The change in potential energy due to this displacement is

$$du = +dW = -q \times E \times dx.$$

The change in potential is  $dV = \frac{du}{a}$  i.e. dV = -E dx.

[If the test charge is moved along the field,  $dV = E \times dx$  (as shown in article 1.8).] Integrating between  $x_1$  and  $x_2$ , we get

$V_2 - V_1 = -\int_{x_1}^{x_2} E dx$ , where  $V_2$  and  $V_1$  are the potentials at  $x_2$  and  $x_1$  respectively.

If we select point  $x_1$  as reference having zero potential, we can write V(r) =

$-\int_{\infty}^{x} E \cdot dx$ , where x is distance equal to  $x_2$ .

# 1.14 ELECTRIC FIELD INSIDE A CONDUCTOR

When there is no electric field around a conductor the conduction electrons are almost uniformly distributed within the conductor. In any small volume of the conductor the number of electrons is equal to the number of proton in the nuclei of each atom of the conductor. The net charge in the volume is then zero. Next we suppose that an electric field E is created in the direction left to right across the conductor. This field will exert a force on the free electrons in the atoms of the conductor from right to left. The free electron then move towards the left and consequently the number of electrons in the left will increase while the number of electrons in the right decreases. The left side of the conductor then becomes negatively charged while the right side is positively charged. The electron continue to drift towards the left. The result is the creation of an electric field of strength  $E\phi$  within the conductor in the direction opposite to the applied field. With passage of time a situation comes when the field E' inside the conductor is equal to the magnitude of the external field E. The net electric field inside the conductor is zero. Then a steady state is reached when some positive and negative charges appear at the surface of the conductor while there is no electric field inside the plate. Thus there is no electric field inside the conductor when it is subjected to an external electric field. The redistribution of electrons take place in such a way that charges remain at the surface of the conductor only.

It may be recalled here from the basic concepts of physics that in conductors there is always existence of free electrons while in insulators all atomic electrons are tightly bound to their respective nuclei. When insulators are placed in an electric field they may slightly shift their parent position but cannot drift from their parent atoms and hence cannot move long distance. These materials are then said to act as dielectrics. If the external field is strengthened further, a time will come when the bonding of the electron with their nuclei may break causing them to drift apart. We call this phenomenon as breakdown of dielectric medium.

# I.1.10 Basic Electrical and Electronics Engineering–II

#### 1.15 CONTINUOUS CHARGE DISTRIBUTION

It is impractical to work in terms of discrete charges and we need to work with continuous charge distributions. It is impractical to specify the charge distribution on the surface of a charged conductor in terms of the locations of the microscopic charged constituents. It is more logical to consider an area element  $\Delta S$  on the surface of the conductor (which is very small on the macroscopic scale but large enough to include a very large number of electrons) and specify the charge  $\Delta Q$  on that element. The surface charge density can be defined as

$$\delta = \frac{\Delta Q}{\Delta S}$$

The unit of  $\delta$  is C/m<sup>2</sup>. The surface charge density  $\delta$  ignores the quantisation of charge and the discontinuity in charge distribution at the microscopic level.  $\delta$  represents the macroscopic surface charge density which is a smoothed average of the microscopic charge density over an area element  $\Delta S$  which is large microscopically but small macroscopically.

Similarly, we can define linear charge density  $\lambda$  and volume charge density  $\rho$ .

$$\lambda = \frac{\Delta Q}{\Delta l}$$

where  $\Delta l$  is a small line element of wire on the macroscopic scale which, however, includes a large number of microscopic charged constituents and  $\Delta Q$  is the charge contained in that line element. The unit for  $\lambda$  is c/m.

Now,

$$\rho = \frac{\Delta Q}{\Delta V}$$

where  $\Delta Q$  is the charge included in the macroscopically small volume element  $\Delta V$  that includes a large number of microscopic charged constituents. Unit of  $\rho$  is c/m<sup>3</sup>.

Now, suppose a continuous charge distribution in space has a charge density  $\rho$ . The charge distribution is divided into small volume elements of size  $\Delta V$ . The charge in volume element  $\Delta V$  is  $\rho \Delta V$ . Then the electric field at any general point *P* due to the charge  $\rho \Delta V$  is given by Coulomb's law:

$$\Delta E = \frac{\rho \Delta V}{4\pi \varepsilon_o r^2}$$

where r is the distance between the charge element and P. By the Superposition principle, the total electric field due to the charge distribution is obtained by adding over electric fields due to different volume elements:

$$E = \frac{1}{4\pi\varepsilon_o} \sum_{\Delta V} \frac{\rho \Delta V}{r^2}$$

By using Coulomb's law and the Superposition principle, electric field can be determined for any charge distribution, discrete or continuous, or part discrete and part continuous.

Electrostatics

# 1.16 GAUSS'S LAW AND ITS DERIVATION

Statement of Gauss's Law The flux of the net electric field through a closed surface is equal to the net charge enclosed by the surface divided by  $\varepsilon_0$ .

i.e.,

$$\oint E \cdot ds = \frac{q_{\rm in}}{\varepsilon_o}$$

(1.18)

where  $\oint E \cdot ds$  represents the flux  $\phi$  through a closed

surface and  $q_{in}$  is the net charge enclosed by the surface through which the flux passes.

**Derivation of Gauss's Law from Coulomb's Law** Let us suppose that a charge q is placed at a point O inside a closed surface (Fig. 1.5). We assume a point P on the surface and consider a small area Ds on the surface around P.

Let OP = x.

The electric field at point P due to the charge q is given by,  $E = q/4\pi\varepsilon_o \cdot x^2$ , directed along the line OP.

Let us suppose this line OP makes an angle  $(\theta)$  with the outward normal to the surface  $\Delta s$ . The flux of the electric field through  $\Delta s$  is given by

$$Df = E \Delta s \cos q$$

$$= \frac{q}{4\pi\varepsilon_o x^2} \cdot \Delta s \cos q$$

$$= \frac{q}{4\pi\varepsilon_o} \cdot \Delta s$$

where  $\Delta \sigma = \frac{\Delta s \cdot \cos \theta}{x^2}$  [Actually ( $\Delta \sigma$ ) is the solid angle subtended by ( $\Delta s$ ) at O]

$$\therefore \qquad f = \sum \frac{q}{4\pi\varepsilon_o} \cdot \mathrm{D}s = \frac{q}{4\pi\varepsilon_o} \sum \Delta\sigma$$

We can see that  $[S(D_s)]$  represents the sum that is actually the total solid angles subtended by a closed surface at *O*. Obviously this total solid angle is 4p.

: the total flux of the electric field due to the internal charge q through the closed surface is

$$f = \frac{q}{4\pi\varepsilon_o} \cdot 4\pi = \frac{q}{\varepsilon_o}$$

$$\phi \equiv \oint E \cdot ds \text{, hence we have}$$

$$\oint E \cdot ds = \frac{q_{\text{in}}}{\varepsilon_o} \text{ (proof of Gauss's law)}$$

(1.19)

$\cdot \cdot$

face

a closed sur-

I.1.11

# I.1.12 Basic Electrical and Electronics Engineering–II

where,  $\frac{q_{\text{in}}}{\varepsilon_o} = \sum \frac{q_i}{\varepsilon_o}$  (i.e. the sum of all charges  $q_1, q_2, ..., q_i, ..., q_n$  located in the

said closed surface. We do not consider external charges as the solid angle (Ds) subtended by a closed surface at any external point is zero, then f becomes zero.

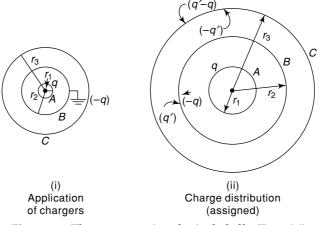

# 1.17 APPLICATIONS OF GAUSS'S LAW

The electric field for symmetric charge configurations can be obtained in a simple way using Gauss's law. This can be understood by considering the following cases

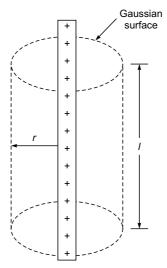

# 1.17.1 Field due to an Infinitely Long Straight Uniformly Charged Wire

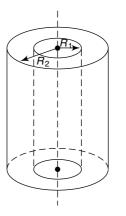

Consider an infinitely long thin straight wire with uniform linear charge density  $\lambda$ . To calculate the field, imagine a cylindrical Gaussian surface with radius r as shown in Fig. 1.6. The wire is obviously an axis of symmetry. Since the field is everywhere radial, flux through the two ends of the cylindrical Gaussian surface is zero. At the cylindrical part of the surface, E is normal to the surface at every point and its magnitude is constant, since it depends only on r. The surface area of the curved part is  $2\pi rl$ , where l is the length of the cylinder.

Flux through the Gaussian surface

- = Flux through the curved cylindrical part of the surface

- $= E \times 2\pi rl$

The surface includes charge equal to  $\lambda l$  where  $\lambda$  is the linear charge density in the wire in c/m. According to Gauss's law,

Fig. 1.6 Gaussian surface for a long thin wire of uniform linear charge density

$$E \times 2\pi r l = \lambda l / \varepsilon_o$$

$$E = \frac{l}{2\pi \varepsilon_o r}$$

or

It may be noted that though only the charge enclosed by the surface  $(\lambda l)$  was included above, the electric field *E* is due to the charge on the entire wire. Also, we have to assume that the wire is infinitely long. Otherwise, we cannot take *E* to be normal to the curved part of the cylindrical Gaussian surface. Equation (1.20) is approximately true for an electric field around the control portions of a long wire, where the end effects may be ignored.

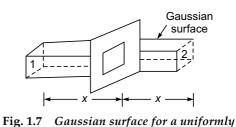

# 1.17.2 Field due to a Uniformly Charged **Infinite Plane Sheet**

Let  $\delta$  be the uniform surface charge density of an infinite plane sheet as shown in Fig. 1.7. By symmetry, the electric field will not depend on y and z coordinates and its direction at every point must be parallel to the *x*-direction.

We consider a Gaussian surface to be a rectangular parallelpiped of

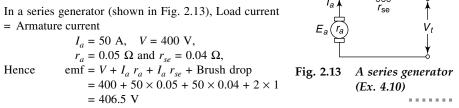

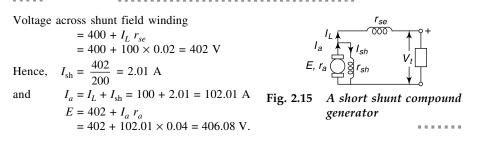

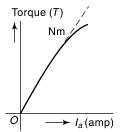

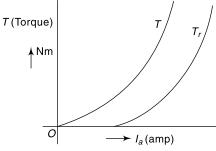

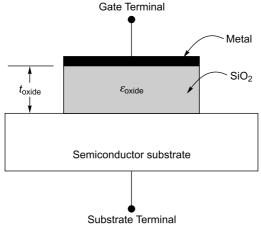

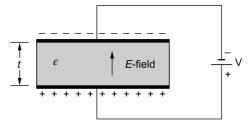

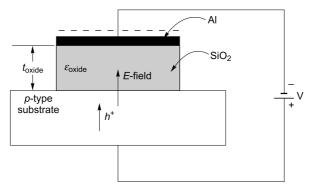

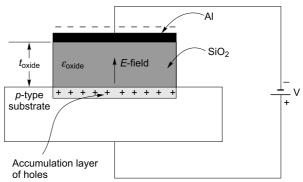

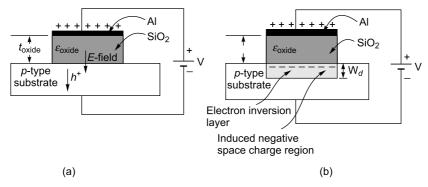

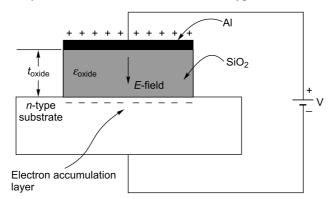

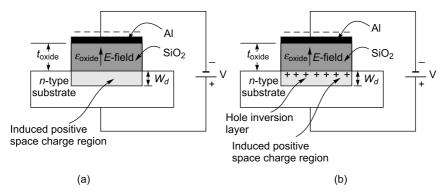

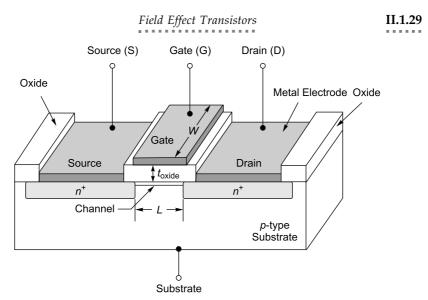

not contribute to the total flux.